# SG1010 StarFabric Switch

# Hardware Reference Manual

Revision Information: Revision 2.0 15 October 2004

StarGen, Inc., 225 Cedar Hill Street, Suite 22, Marlborough, MA 01752 www.stargen.com

#### October 2004

StarGen, Inc. believes the information in this publication is correct; however, the information is subject to change without notice.

StarGen, Inc. does not claim that the use of its products in the manner described in this publication will not infringe on any existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

©StarGen, Inc. 2000, 2004. All rights reserved. Printed in U.S.A.

StarGen, StarFabric, and the STARGEN logo are trademarks of StarGen, Inc.

SPI is a trademark of Motorola, Inc. All other trademarks and registered trademarks are the property of their respective owners.

# Contents

# Preface

# 1 Introduction

# 2 Feature Summary

| 2.1 | Scalability and Performance1               |

|-----|--------------------------------------------|

| 2.2 | Compatibility                              |

| 2.3 | Quality of Service                         |

| 2.4 | Reliability, Availability, Serviceability1 |

| 2.5 | Additional Features                        |

# 3 Operation

| 3.1       | Routing and Address Decoding                                   | <br> | 3    |

|-----------|----------------------------------------------------------------|------|------|

| 3.1.1     | Address Models                                                 |      |      |

| 3.1.1.1   | StarFabric Address Model                                       | <br> | 3    |

| 3.1.1.2   | PCI Addressing Model                                           | <br> | 3    |

| 3.1.2     | Path Routing                                                   |      |      |

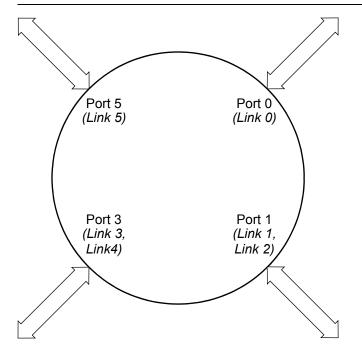

| 3.1.2.1   | Link and Port Configurations                                   |      |      |

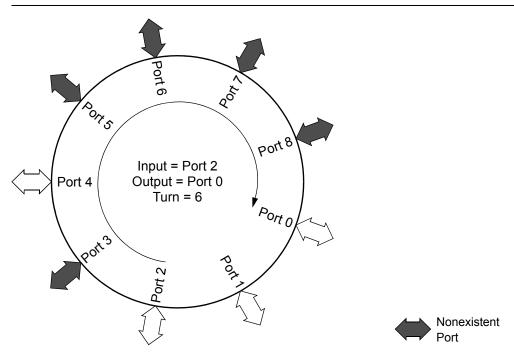

| 3.1.2.2   | Path Routing through Turn Specifications                       | <br> | 5    |

| 3.1.2.3   | Path-Routing Errors                                            |      |      |

| 3.1.2.4   | Path-routed CSR Frames to SG1010                               |      |      |

| 3.1.2.4.  | Register Path Protection                                       | <br> | 7    |

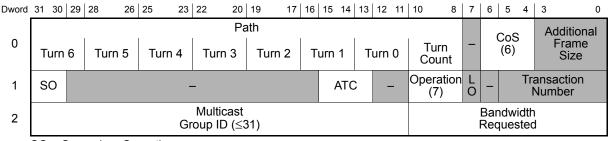

| 3.1.3     | Multicast Routing                                              | <br> | 7    |

| 3.1.3.1   | Sending Multicast Frames                                       |      |      |

| 3.1.3.2   | Multicast Acknowledges                                         | <br> | 9    |

| 3.1.3.3   | Tracking Multicast Acknowledge with Failures (Multicast Nacks) | <br> | . 10 |

| 3.1.3.4   | Configuring Multicast Groups and Bandwidth Allocation          | <br> | . 11 |

| 3.1.3.4.  | Bandwidth Allocation                                           | <br> | 11   |

| 3.1.3.4.2 | 2 Joining Multicast Groups and Allocating Bandwidth            | <br> | . 11 |

| 3.1.3.4.3 | 3 Exiting Multicast Groups and Restoring Bandwidth             | <br> | . 13 |

| 3.1.3.4.4 | Tearing Down Multicast Groups                                  | <br> | . 14 |

| 3.1.4     | Address Routing                                                | <br> | . 14 |

| 3.1.4.1   | Smart Address Routing                                          | <br> | 16   |

| 3.1.4.2   | Downstream Address Routing                                     | <br> | . 16 |

| 3.1.4.3                           | Upstream and Peer-to-Peer Address Routing            | 16 |

|-----------------------------------|------------------------------------------------------|----|

| 3.1.4.4 PCI Configuration Routing |                                                      |    |

| 3.1.4.4.1                         | Type0 Configuration Register Accesses                |    |

| 3.1.4.4.2                         | Type1 Downstream Configuration Frames                |    |

| 3.1.4.4.3                         | Upstream and Peer-to-Peer Type1 Configuration Frames |    |

| 3.1.4.5                           | Address-routed Memory Frame Decoding and Routing     |    |

| 3.1.4.5.1                         | Downstream Memory Frames                             |    |

| 3.1.4.5.2                         | Upstream and Peer-to-Peer Memory Frames              |    |

| 3.1.4.5.3                         | 64-bit Addressing                                    |    |

| 3.1.4.6                           | PCI I/O Decoding                                     |    |

| 3.1.4.6.1                         | Downstream I/O Frames                                |    |

| 3.1.4.6.2                         | Upstream and Peer-to-Peer I/O Frames                 |    |

| 3.1.5                             | Generating Address-Routed Response Frames            | 22 |

| 3.2 Lir                           | ne Credits                                           | 22 |

| 3.2.1                             | Line Credit Types                                    |    |

| 3.2.2                             | Line Credit Initialization.                          |    |

| 3.2.3                             | Line Credit Reallocation                             |    |

| 3.2.4                             | Using Line Credits.                                  |    |

| 3.2.5                             | Returning Line Credits to Link Partners              |    |

| 3.2.5.1                           | Bulk Credit Frames.                                  |    |

| оо <b>г</b>                       | ana Ardaving and Arbitration                         | 20 |

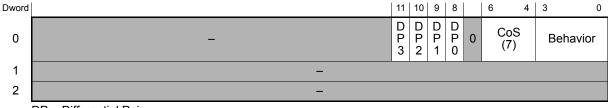

| <b>3.3 Fra</b> 3.3.1              | ame Ordering and Arbitration                         |    |

|                                   | Frame Ordering Rules                                 |    |

| 3.3.2                             | Frame Arbitration                                    |    |

| 3.3.2.1                           | Frame Arbitration Groups                             |    |

| 3.3.2.2                           |                                                      |    |

| 3.3.2.3                           | CoS Arbitration                                      |    |

| 3.3.2.4                           | Path-routed Turn and Multicast Group Arbitration     | 28 |

| 3.4 Ev                            | ents                                                 | 28 |

| 3.4.1                             | Event Tables                                         |    |

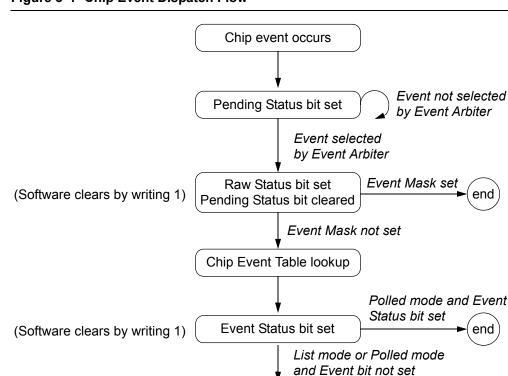

| 3.4.2                             | Chip Events.                                         |    |

| 3.4.2.1                           | Pending Events                                       |    |

| 3.4.2.2                           | Event Mask                                           |    |

| 3.4.2.3                           | Raw Event Status                                     |    |

| 3.4.2.4                           | Chip Event Table Lookup and Event Status Register    |    |

| 3.4.2.5                           | Using Polled vs. List Modes                          |    |

| 3.4.2.6                           | Routing Events                                       |    |

| 3.4.3                             | Path Events                                          |    |

| 3.4.4                             | Event Dispatch without Event Tables                  |    |

| 3.4.5                             | Signal Events                                        |    |

| 3.4.6                             | Event Codes                                          | 35 |

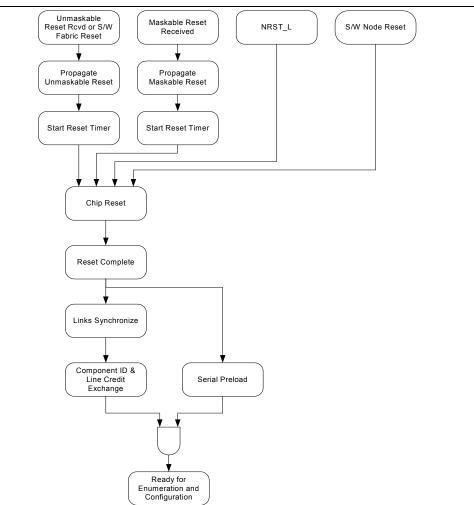

| 3.5 Re                            | set and Initialization                               | 36 |

| 3.5.1                             | Reset.                                               |    |

| 3.5.1.1                           | Reset Propagation                                    |    |

| 3.5.1.1.1                         | Sending Propagating Resets                           |    |

| 3.5.1.1.2                         | Receiving Propagating Resets                         | 40 |

| 3.5.2                             | Serial ROM Preload                                   |    |

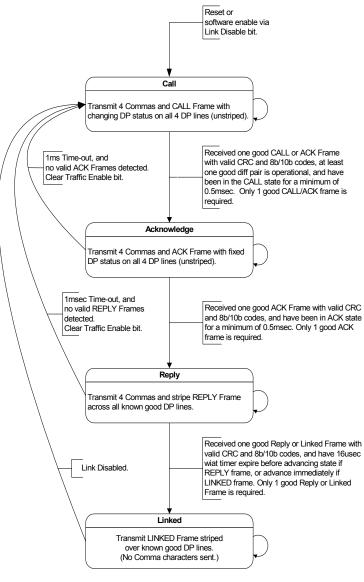

| 3.5.3                             | Link Synchronization.                                |    |

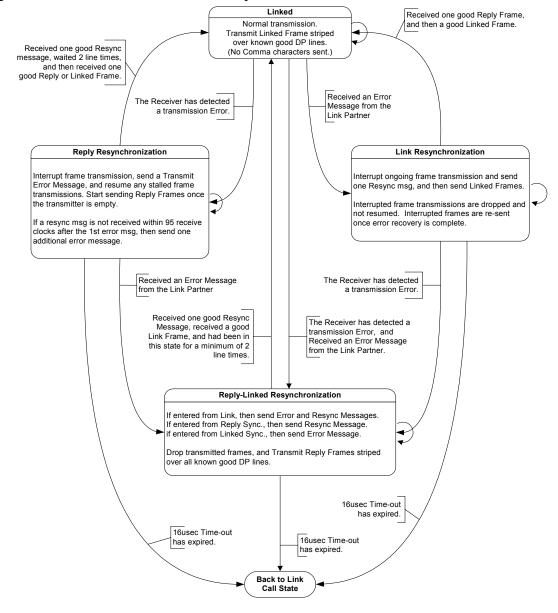

| 3.5.3.1                           | Call State                                           |    |

| 3.5.3.2                           | Acknowledge State                                    |    |

| 3.5.3.3                           | Reply State.                                         |    |

| 3.5.3.4                           | Linked State                                         |    |

| 3.5.3.5                           | Disabling a Link                                     | 43 |

|                                   |                                                      |    |

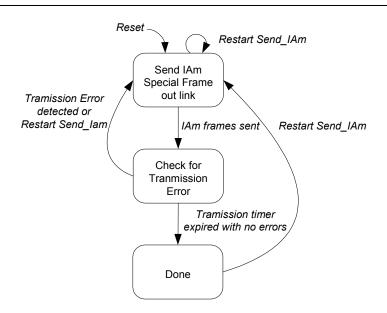

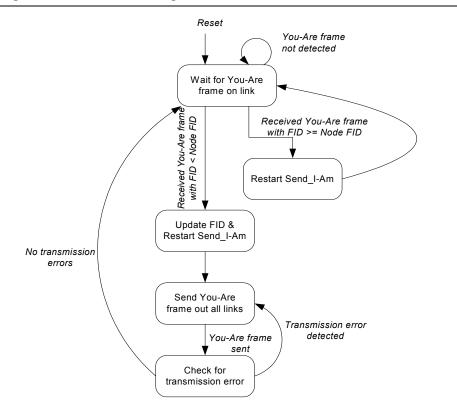

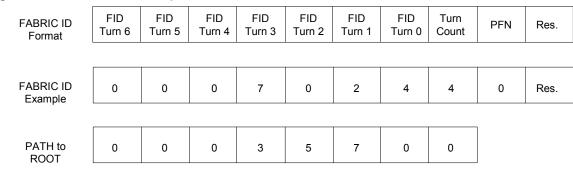

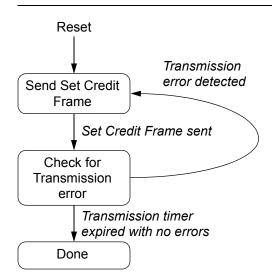

| 3.5.3.6<br>3.5.4<br>3.5.4.1<br>3.5.4.2<br>3.5.4.3<br>3.5.4.4<br>3.5.5<br>3.5.5.1<br>3.5.6                                                                         | Clock Comma Propagation.<br>Fabric Enumeration.<br>Component Identification<br>Fabric ID Assignment.<br>Using the Fabric ID as a Path to the Root<br>Line Credit Initialization<br>PCI Configuration<br>Port Map Table Initialization.<br>Root Port Modification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 44<br>. 45<br>. 46<br>. 48<br>. 49<br>. 51<br>. 51                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3.6</b><br>3.6.1                                                                                                                                               | Link and Port Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

| 3.6.1.1                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

| 3.6.1.2                                                                                                                                                           | Link Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 53                                                                                                                                                         |

| 3.6.1.3                                                                                                                                                           | Fragile Links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                              |

| 3.6.1.4<br>3.6.1.5                                                                                                                                                | Port Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |

| 3.6.2                                                                                                                                                             | Sending Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                              |

| 3.6.2.1                                                                                                                                                           | Empty Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 55                                                                                                                                                         |

| 3.6.2.2                                                                                                                                                           | Frame Sequence Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                              |

| 3.6.2.3<br>3.6.2.3.                                                                                                                                               | Transmission Errors       Image: Construction of the second |                                                                                                                                                              |

| 3.6.2.3.                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

| 3.6.2.4                                                                                                                                                           | Using Change Thread Frames When a Link Goes Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                              |

| 3.6.2.5                                                                                                                                                           | Kill Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 59                                                                                                                                                         |

| 3.7                                                                                                                                                               | Software Generated Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 59                                                                                                                                                         |

|                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                              |

|                                                                                                                                                                   | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60                                                                                                                                                         |

| 3.8.1                                                                                                                                                             | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>. 60</b><br>. 61                                                                                                                                          |

| 3.8.1<br><b>3.9</b>                                                                                                                                               | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . <b>60</b><br>. 61<br>. <b>61</b>                                                                                                                           |

| 3.8.1<br><b>3.9</b><br><b>3.10</b>                                                                                                                                | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 61                                                                                                                                 |

| 3.8.1<br>3.9<br>3.10<br>3.10.1                                                                                                                                    | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62                                                                                                                         |

| 3.8.1<br><b>3.9</b><br><b>3.10</b>                                                                                                                                | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62                                                                                                                 |

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.1                                                                                                                        | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62                                                                                                         |

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3                                                                                        | Semaphore Registers<br>Semaphore Frames<br>General Purpose I/O Interface<br>Serial ROM Interface<br>ROM Programming Interface<br>Writing through the ROM Register Interface<br>Reading through the ROM Register Interface<br>Vital Product Data (VPD)<br>Serial ROM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63                                                                                         |

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1                                                                            | Semaphore Registers<br>Semaphore Frames<br>General Purpose I/O Interface<br>Serial ROM Interface<br>ROM Programming Interface<br>Writing through the ROM Register Interface<br>Reading through the ROM Register Interface<br>Vital Product Data (VPD)<br>Serial ROM Interface<br>Serial Address and Data Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64                                                                         |

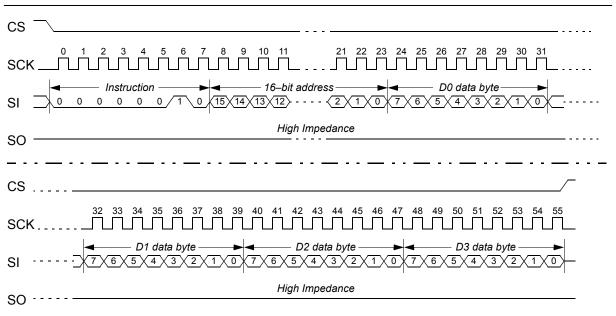

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1<br>3.10.3.2                                                                | Semaphore Registers<br>Semaphore Frames<br>General Purpose I/O Interface<br>Serial ROM Interface<br>ROM Programming Interface<br>Writing through the ROM Register Interface<br>Reading through the ROM Register Interface<br>Vital Product Data (VPD)<br>Serial ROM Interface<br>Serial Address and Data Organization<br>Serial ROM Write Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 64<br>. 64                                                                 |

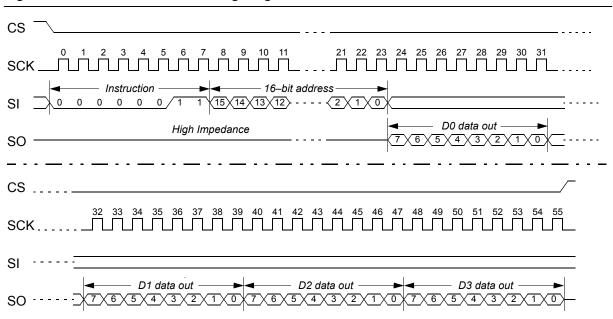

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1                                                                            | Semaphore Registers<br>Semaphore Frames<br>General Purpose I/O Interface<br>Serial ROM Interface<br>ROM Programming Interface<br>Writing through the ROM Register Interface<br>Reading through the ROM Register Interface<br>Vital Product Data (VPD)<br>Serial ROM Interface<br>Serial Address and Data Organization<br>Serial ROM Write Operation.<br>Serial ROM Read Operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64<br>. 64<br>. 65                                                 |

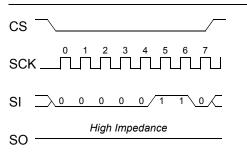

| 3.8.1<br>3.9<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1<br>3.10.3.2<br>3.10.3.3                                                            | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64<br>. 64<br>. 65<br>. 67                                         |

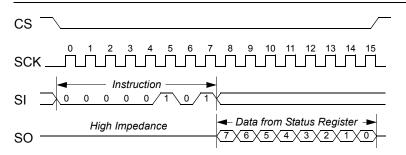

| 3.8.1<br>3.9<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1<br>3.10.3.2<br>3.10.3.3<br>3.10.3.4<br>3.10.3.5<br><b>3.11</b>                     | Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64<br>. 65<br>. 67<br>. 67<br>. 68                         |

| 3.8.1<br>3.9<br>3.10<br>3.10.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1<br>3.10.3.2<br>3.10.3.3<br>3.10.3.4<br>3.10.3.5<br><b>3.11</b><br>3.11.1               | Semaphore Registers .<br>Semaphore Frames<br>General Purpose I/O Interface<br>Serial ROM Interface .<br>ROM Programming Interface .<br>Writing through the ROM Register Interface .<br>Reading through the ROM Register Interface .<br>Vital Product Data (VPD) .<br>Serial ROM Interface .<br>Serial Address and Data Organization .<br>Serial ROM Write Operation .<br>Serial ROM Write Operation .<br>Serial ROM Write Enable Operation .<br>Serial ROM Read Status Register Operation .<br>Serial ROM Read Status Register Operation .<br>Serial ROM Read Status Register Operation .<br>JTAG .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64<br>. 65<br>. 67<br>. 67<br>. 68<br>. 68                 |

| 3.8.1<br>3.9<br>3.10.1<br>3.10.1.1<br>3.10.1.2<br>3.10.2<br>3.10.3<br>3.10.3.1<br>3.10.3.2<br>3.10.3.3<br>3.10.3.4<br>3.10.3.5<br><b>3.11</b><br>3.11.1<br>3.11.2 | Semaphore Registers         Semaphore Frames         General Purpose I/O Interface         Serial ROM Interface         ROM Programming Interface         Writing through the ROM Register Interface         Reading through the ROM Register Interface         Vital Product Data (VPD)         Serial ROM Interface         Serial ROM Write Operation         Serial ROM Read Operation         Serial ROM Write Enable Operation         Serial ROM Read Status Register Operation         Serial ROM Read Status Register Operation         Serial ROM Read Status Register Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 60<br>. 61<br>. 61<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 62<br>. 63<br>. 63<br>. 63<br>. 64<br>. 65<br>. 67<br>. 67<br>. 68<br>. 68<br>. 68         |