# Dolphin PCI Express MXH932 Adapter

MXH932 Transparent Adapter Users Guide Version 3.0

Date: 6<sup>th</sup> January 2025

# **Table of Contents**

| DISCLAIMER                                                             | 4  |

|------------------------------------------------------------------------|----|

| TERMS AND ACRONYMS                                                     | 5  |

| MXH932 HIGH LEVEL SPECIFICATION                                        | 6  |

| MTBF BY TEMPERATURE AND ENVIRONMENT                                    | 7  |

| PACKAGING                                                              |    |

| PRE-INSTALLATION QUESTIONS                                             |    |

| PCIE SLOT DETERMINATION                                                | Q  |

| MXH932 Host / Target Configuration                                     |    |

| AIRFLOW - OPERATING ENVIRONMENT                                        |    |

| CABLE CONNECTIONS.                                                     |    |

| PCI Express 4.0 Cables                                                 |    |

| Active Optical PCIe Cables (AOC)                                       |    |

| CMI Functionality                                                      |    |

| INSTALLATION                                                           |    |

|                                                                        |    |

| Step 1 - Unpack board                                                  |    |

| STEP 2 - CHANGE PCIE BRACKET IF NECESSARY                              |    |

| STEP 3 - CONFIGURE THE BOARD FOR PROPER OPERATION                      |    |

| Step 4 - Ensure proper Airflow                                         |    |

| Step 5 - Install the Adapter Card                                      |    |

| Step 6 - Installing and Removing the Cable                             |    |

| Connecting the Cable                                                   |    |

| Cable stain relief                                                     |    |

| Supported cable lengths                                                |    |

| Disconnecting the Cable                                                |    |

| STEP 7 - VERIFY INSTALLATION & LEDS                                    |    |

| OPERATION                                                              |    |

| CONFIGURATION AND DIP SWITCHES                                         | 12 |

| DIP Switches                                                           |    |

| Thermal shutdown                                                       |    |

| DIP Switch settings for MXH932 Host operation                          |    |

| DIP Switch settings for MXH932 Target operation                        |    |

| TRANSPARENT USE CASES                                                  | 15 |

| Target Card Clocking Option                                            |    |

| Use Case A - 1 Host – Single Expansion Configuration PCIe x16          |    |

| Use Case B – 1 Host – Single or Dual Expansion Configuration – PCIe x8 |    |

| Use Case C – 1 Host - Quad Expansion Configuration – PCIe x4           |    |

| Use Case D – 1 Host – Transparent fan-out using MXS924 - PCIe x16      |    |

| Use Case E – Multi Host – Transparent fan-out using MXS924 - PCIe x16  |    |

| Use Case F – Transparent Target with two x8 Downstream ports           |    |

| Use Case G – Transparent Target with four x4 Downstream ports          |    |

| EEPROM AND FIRMWARE UPGRADE                                            |    |

| Identifying the Card                                                   |    |

| SUPPORT                                                                | 19 |

| TECHNICAL INFORMATION                                                  | 20 |

| BOARD REVISION HISTORY                          |               |

|-------------------------------------------------|---------------|

| SIMPLIFIED SCHEMATICS                           |               |

| PCIE CABLE PORT SIGNALS                         |               |

| EXTERNAL PCIE X4 CABLE CONNECTOR PIN-OUT        |               |

| PCIE CABLE PORT MAPPING                         |               |

| MXH932 PCIe x16 Edge Connector Pin-Out          |               |

|                                                 |               |

| COMPLIANCE AND REGULATORY TESTING               | 23            |

| COMPLIANCE AND REGULATORY TESTING               |               |

| LIMITED WARRANTY                                | <b>24</b><br> |

| LIMITED WARRANTY<br>Warranty Period<br>Coverage | <b>24</b><br> |

| LIMITED WARRANTY                                | <b>24</b><br> |

### DISCLAIMER

DOLPHIN INTERCONNECT SOLUTIONS RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY OF ITS PRODUCTS TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN.

DO NOT USE INFORMATION IN THIS GUIDE TO DESIGN YOUR OWN PCI-SIG COMPLIANT PRODUCT, ALWAYS REFERENCE THE ORIGINAL PCI-SIG SPECIFICAITON FOR DETAILS.

TO THE FULLEST EXTENT PERMITTED BY LAW, DOLPHIN WILL NOT BE LIABLE FOR ANY INDIRECT, INCIDENTAL, SPECIAL OR CONSEQUENTIAL DAMAGES (INCLUDING LOST PROFITS, LOST DATA, OR LOSS OF USE) ARISING OUT OF ANY USE OF DOLPHIN'S PRODUCTS, SOFTWARE OR SERVICE PROVIDED. DOLPHIN'S MAXIMUM LIABILITY WILL NOT EXCEED THE TOTAL AMOUNT PAID FOR THE PRODUCT BY THE PURCHASER.

PCI Express External Cabling specification 3.0 is, as of the release of MXH932, not completed and ratified by the PCI-SIG. The MXH932 is designed to the new specification, but Dolphin cannot guarantee the card will be compliant to the final 3.0 version. Dolphin firmware tools can update the CMI implementation.

### LIFE SUPPORT POLICY

DOLPHIN INTERCONNECT SOLUTIONS' PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES.

### **ENVIRONMENTAL POLICY**

Dolphin is minimizing the amount of printed documentation and software CDs in its shipments; please download additional documentation and software from www.dolphinics.com.

### Scope

This version of the MXH932 Users Guide is valid for firmware version 12.

# **Terms and Acronyms**

Important terms and acronyms used in this manual

| AOC            | Active Optical Cable. PCIe fiber cable assembly available from Dolphin.                                                                                                                                                                                |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СМІ            | <b>C</b> able <b>M</b> anagement Interface. The 2-wire management interface for communication between subsystems connected by a PCIe 4.0 cable. Details can be found in the PCI-SIG External Cabling Specification 4.0.                                |

| ВМС            | Board Management Controller - Microcontroller on the MXH932 used to manage and implement CMI communications.                                                                                                                                           |

| eXpressWare    | Dolphin's software stack for PCIe clustering and IO. Please visit <u>www.dolphinics.com/software</u> for more information.                                                                                                                             |

| Host mode      | The card is installed in a root complex / Host PC.                                                                                                                                                                                                     |

| Hot Add        | Attaching an IO Expansion system after the server is booted. System dependent. To Hot Add devices utilizing larger resources, the MXH930 card with Dolphins eXpressWare SmartIO extension should be used. Please contact Dolphin for more information. |

| Hot Plug       | PCIe Configuration option to support hot plug events.                                                                                                                                                                                                  |

| Lane           | One PCI Express Lane contains a differential pair for transmission and a differential pair for reception.                                                                                                                                              |

| Link           | A collection of one or more PCI Express Lanes providing the communication path between an Upstream and Downstream Port.                                                                                                                                |

| PCIe 4.0 cable | Cable compliant to the PCI-SIG External Cabling Specification 4.0. Support for CMI.                                                                                                                                                                    |

| Port           | PCIe Cable port. The MXH932 has four x4 ports, named P1, P2, P3, P4. These ports can be merged to two x8 ports, or one x16 port. The physical ports are identified by text on the PCIe brackets.                                                       |

| Target mode    | The card is installed in an expansion chassis / backplane.                                                                                                                                                                                             |

| Wake           | A mechanism used by a downstream device to request the reapplication of main power when in the L2 Link                                                                                                                                                 |

# **MXH932 High Level Specification**

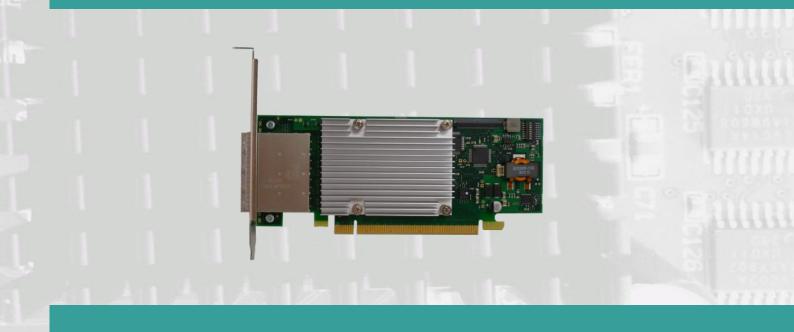

The MXH932 is a low profile, half-length PCIe adapter that can be configured as a Transparent Host Adapter card or a Target adapter card. Once installed in any server's or PC's PCI Express compliant slot, a MXH932 can connect to another MXH932 configured for Transparent Target operation or any target device compliant to the PCI Express External Cabling Specification 4.0. The MXH932 configured as a Transparent Target card can be installed in a PCI Express compliant expansion upstream slot. Please contact Dolphin for a list of compliant expansion chassis. The MXH932 supports PCIe Gen1, Gen2, Gen3 and Gen4 speeds and x1, x2, x4, x8 and x16 link-widths. The card will operate at the highest common speed shared between the slot and the card (Gen4) and the widest common link-width (x16).

- PCI Express Base Specification, Rev. 4.0.

- PCI Express CEM Specification, Rev. 4.0.

- PCI Express External Cabling specification 4.0

- PCI Express Gen4 16.0 GT/s per lane signaling 256 GT/s total signaling.

- PCI Express Gen4 x16 edge connector. The card installs in any PCI Express slot that has a physical x16 connector.

- Compliant with PCI Express Gen1 through Gen3 computers and IO systems, auto detection.

- The MXH932 supports transparent connections to IO systems (Host and Target operation).

- Quad SFF-8644 cable connector

- Durability max total 250 mating cycles

- Cable port configurations, up to

- o One x16

- o Two x8

- o Four x4

•

- Microsemi Switchtec PM40036 PFX PCI Express Gen4 chipset.

- 130 nanosecond cut-through latency port to port.

- Support for PCIe 3.0 and PCIe 4.0 SFF-8644 copper cables with CMI and PCIe Active Optical cables.

- Support for active optical fibers up to 100 meters.

- Low profile, Half-length PCI Express Electromechanical Specification, Rev 4.0.

- Dimensions are 167.65mm (6.600 inches) x 68.90 mm (2.731 inches)

- Comes with both a low profile and a standard profile PCI Express bracket.

- Host clock isolation. Automatic support for host running CFC or SSC mode.

- Prepared for SRIS clocking.

- VAUX powered board management controllers for flexible configuration and cable management.

- Flash recovery option. PFX Multiconfiguration support.

- Maximum power ratings:

- 12 Volt: 1.66 A (no port power) 2.66 A (max port power)

- +3.3 Volt: Not connected

- +3.3 Vaux: 100 mA

- Typical power ratings:

- 12 Volt: 1.5 A (no port power)

- +3.3 Volt: Not connected

- +3.3 Vaux: 100 mA

- Port power supply (per cable port):

- VPWR: 3.2V 3.4V, 0.86 A

- VMGTPWR: 3.2V 3.4V, 89 mA

- Operating Temperature: 0°C 55°C (32°F 131°F), Airflow: 350 LFM (Preliminary)

- Operating Temperature with AOC: TBD

- Relative Humidity: 5% 95% (non- condensing)

- CE and FCC markings

# **MTBF by Temperature and Environment**

The MTBF (in hours) for the MXH932 can be found in the table below. The numbers are calculated using the Telcordia SR-332 issue 2 (2006) standard.

| Ambient   | Environment              |                               |                  |

|-----------|--------------------------|-------------------------------|------------------|

| Temp [°C] | Ground fixed, controlled | Ground fixed,<br>uncontrolled | Ground<br>mobile |

| 0         | 4.101.016                | 2.050.508                     | 683.503          |

| 5         | 3.543.448                | 1.771.724                     | 590.575          |

| 10        | 3.028.513                | 1.514.257                     | 504.752          |

| 15        | 2.560.400                | 1.280.200                     | 426.733          |

| 20        | 2.141.924                | 1.070.962                     | 356.987          |

| 25        | 1.774.116                | 887.058                       | 295.686          |

| 30        | 1.456.142                | 728.071                       | 242.690          |

| 35        | 1.185.515                | 592.758                       | 197.586          |

| 40        | 958.455                  | 479.227                       | 159.742          |

| 45        | 770.360                  | 385.180                       | 128.393          |

| 50        | 616.260                  | 308.130                       | 102.710          |

| 55        | 491.191                  | 245.595                       | 81.865           |

Table 1: MTBF vs. Temperature and Environment

# **Packaging**

The MXH932 includes the following components.

- MXH932 Adapter Board with full height profile PCIe bracket mounted

- Low profile PCIe bracket

- Anti-static bag

- Getting started guide

### **Pre-Installation Questions**

Certain steps should be taken prior to installing the MXH932. You should determine the following configuration requirements.

- Which PCIe slot and system will the card be installed in?

- Will the board act as a host adapter or target adapter?

- What is the speed and link width of the slot that the card will be installed in?

- What is the operating environment in which the card will be installed?

- What type and length of cables will be used?

- How to establish proper operational conditions, temperature, and airflow.

### **PCIe Slot Determination**

The MXH932 supports PCIe Gen1, Gen2, Gen3 and Gen4 speeds and x1, x2, x4, x8 and x16 link-widths. The slot width and speed will affect the performance of the card. The card can be physically installed in a x4, x8 or x16 connector. The card will auto configure to the slot speed and width.

### **MXH932 Host / Target Configuration**

The MXH932 can act as either a host adapter or target adapter. The MXH932 has a DIP switch bank to control these functions. The DIP switch labeled SW1 can be found close to the upper edge of the board. The main configuration options are host or target operations. The default DIP switch setting is transparent host x16 operations. Additional settings are target operations, two x8 links, four x4 links, alternativce edge clock routing and quad edge target.

### **Airflow - Operating Environment**

To maximize lifetime for the product and maintain the warranty, please honor the specified operating temperature and make sure the specified air flow is present. Special care should be considered when the MXH932 is used in office type cabinets in combination with other high energy consuming PCIe devices, e.g. not active-cooled GPUs:

Operating Temperature: 0°C - 55°C (32°F - 131°F), Airflow: 350 LFM (Preliminary) Operating Temperature with AOC: TBD

**TIP:** After installing the Dolphin eXpressWare Board Management software, you can use the tool dis\_diag to determine the actual board temperatures.

**NOTE:** The MXH932 link LEDs will start flashing yellow when a PCIe switch temperature of 95°C (203°F) is reached or when the AOC has reached the max operating temperature. Please consult the AOC data sheet for details.

**NOTE:** The MXH932 card includes overheat protection. The BMC will automatically shut down the MXH932 card if a PCIe switch temperature beyond 105°C (221°F) is detected. Similarly, if an AOC is plugged in, the MXH930 card will automatically shut down if the max operating temperature announced by the connected AOC is violated by 15°C (59°F). Please consult the AOC data sheet for details. The automatic shutdown can be disabled by setting DIP-Switch OPT6.

NOTE: Operating the card or AOC above the maximum specified operating temperature will void the warranty.

NOTE: If the card shuts down due to an overtemperature situation – you must improve the cooling before completely power cycling the system.

### **Cable Connections**

The MXH932 is designed to support both long and short PCIe copper cables as well as PCIe active optical cables (AOC).

The MXH932 cable ports are compliant to the SFF-8644 industry specification and supports PCIe cables compliant to the PCIe External Cabling Specification 4.0. Four x4 cables are needed for full PCIe x16 connectivity.

#### **PCI Express 4.0 Cables**

When used with cables compliant to the new PCIe External Cable standard 4.0, the MXH932 card will initialize CMI communication to the link partner. The card can be connected to an MXH932 in Target mode or any PCIe device compliant to the new cable standard.

### **Active Optical PCIe Cables (AOC)**

Dolphin offers active optical PCIe fiber cables up to 100 meters for the MXH932 cards. CWAKE and CPOWERON is not supported when using standard AOC cables. Please note: Long fiber optic cables will affect latency and throughput. Each meter adds 4-5 nanoseconds of latency.

### **CMI Functionality**

The MXH932 BMC firmware release 2.8 and newer supports the following CMI operations:

- Publishes card and CMI status information in readable memory map

- Supports sending and receiving CMI reset, wake and power status messages

- Supports receiving indicators (LED/messages).

# Installation

### Step 1 - Unpack board

The MXH932 card is shipped in an anti-static bag to prevent static electricity damage. The card should only be removed from the

bag after ensuring that anti-static precautions are taken. Static electricity from your clothes or work environment can damage your PCI Express adapter card or your PC. Always wear a grounded anti-static wrist strap while opening the PC and when the MXH932 is removed from the anti-static bag.

Unpack the MXH932 from the anti-static bag using proper anti-static procedures.

### Step 2 - Change PCIe Bracket if necessary

The MXH932 package includes a standard and low-profile PCI Express bracket. By default, the standard height bracket is installed on the board. If you need to replace the mounted bracket with a low-profile bracket, carefully unscrew the two mounting screws to remove the full height bracket. Save the two mounting screws and replace the bracket with the low-profile bracket. Use the two mounting screws to install the low-profile bracket. The screws should be carefully tightened but be careful not to overtighten. Make sure you are properly grounded to avoid static discharges that may destroy the adapter card before performing this procedure.

# Step 3 - Configure the Board for Proper Operation

Set the DIP switch settings for proper operation depending on the firmware. Please refer to the section Configuration and DIP Switches on page 12 for details.

### Step 4 - Ensure proper Airflow

Please pay proper attention to ensure the selected server / slot position provides the minimum required airflow.

TIP: Immediately after software installation, please use the dis\_diag tool to verify the temperature. If the chip temperature reported by dis diag exceeds 95°C, it is strongly recommended to improve the airflow.

NOTE: Operating the card or AOC above the maximum specified operating temperature will void the warranty.

### Step 5 - Install the Adapter Card

Before installing the adapter card, make sure you are properly grounded to avoid static discharges that may destroy your computer or the adapter card. Ensure you are properly grounded before opening your computer or the anti-static bag containing the MXH932. Please follow your computers or expansion chassis manual on how to install a PCI Express card.

The MXH932 Adapter card can be installed into any PCI Express x16 slot. The MXH932 supports PCI Express Gen1, Gen2, Gen3 and Gen4 signaling. NOTE: A Gen3 slot is recommended as it typically doubles the performance compared to a Gen2 slot. The MXH932 is an x16 card, so maximum performance will only be attained if the slot provides full electrical x16 signaling.

The MXH932 supports hosts using either spread spectrum or constant frequency clocking. The card implements clock isolation.

# Step 6 - Installing and Removing the Cable

Installing and removing cables should be done with both host and expansion system powered off. Please contact your Dolphin representative if you intend to continuously connect and disconnect the PCI Express cables.

### **Connecting the Cable**

Please carefully install the cable connector into the connector housing on the MXH932 adapter card. Cable port 1 is located at the top of the PCIe bracket, ref Figure 1 PCIe Bracket to the right. To install the cable, match the cable house with the connector on the MXH932 adapter card. Use even pressure to insert the connector until it is secure. Adhere to ESD guidelines when installing the cables to ensure you don't damage the board. Note that for wider than x4 connections, the same cable-ports (i.e. port 1 to port 1, port 2 to port 2

through port 4) should be used on both host and target for each individual cable, to ensure that the cards properly link up as x8 or x16.

#### **Cable stain relief**

Strain-relief on the PCIe cables are important to protect the PCIe card from fatigue loading and damage. The cable should be mechanically connected to the rack or cabinet. This is especially important for long heavy cables and cables going between cabinets and racks.

#### Supported cable lengths

The MXH932 supports both copper and active optical PCIe cables (AOC). Maximum lengths between a MXH932 card and other Dolphin products can be found in Table 2 below.

| Cable - SKU | Speed    | Device | Device                          | Distance         |

|-------------|----------|--------|---------------------------------|------------------|

| PCIe4L-xM   | PCle 4.0 | MXH932 | MXH932                          | Up to 5 meters   |

| PCIe4L-xM   | PCle 4.0 | MXH932 | MXH914-MXH919                   | Up to 5 meters   |

| PCIe4L-xM   | PCle 4.0 | MXH932 | MXP924                          | Up to 5 meters   |

| PCIe4L-xM   | PCle 4.0 | MXH932 | MXS924                          | Up to 2 meters   |

| MSP4M-1M    | PCIe 4.0 | MXH932 | Any Dolphin PCIe 4.0<br>product | Up to 102 meters |

| MTFCFF-xxxM | PCIe 4.0 | MXH932 | Any Dolphin PCIe 4.0<br>product | Up to 100 meters |

**Table 2: Cable Specifications**

#### **Disconnecting the Cable**

Please carefully pull the release tab to release the cable from the locking latches and gently pull the cable out of the connector guides.

### Step 7 - Verify Installation & LEDs

The MXH932 comes with 4 bi-color LEDs which show the corresponding cable port status according to Table 3: LED below.

The LEDs are visible through cut-outs in the PCIe bracket on each side of the cable connector block.

| LED color       | Function                                                                                                      |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|--|

| Off             | No cable installed                                                                                            |  |

| Yellow          | Cable installed; no link                                                                                      |  |

| Yellow blink    | Link reset                                                                                                    |  |

| Yellow blinking | Temperature overheat warning, please immediately improve cooling to avoid thermal damages or system shutdown. |  |

| Green           | Cable installed; link operational                                                                             |  |

| Green blinking  | Link operating at lower speed                                                                                 |  |

Table 3: LED behavior

# Operation

### **Configuration and DIP Switches**

The MXH932 has one bank of 8 DIP switches. The default factory setting for the MXH932 is Transparent Host mode, single (up to x16) link connection.

The MXH932 has DIP switches for setting special modes or operations, the meaning of each DIP switch depends on the loaded firmware. Please carefully read the documentation shipped with the card before modifying any DIP switch settings. Please pay close attention to ON and OFF positions written on the DIP switch.

#### **DIP Switches**

| 7 00         |              |

|--------------|--------------|

| 00 00        | COMO-OPT1    |

|              | N BUD OPT2   |

|              | COMPOPT3     |

|              | LO THE OPT4  |

| 111 × 110    | THE THE OPTS |

| 225 98 mm    | 0 140 OPT6   |

| TALL O I MAN | NIND URES    |

| 1000 2 1 =   | - MO SAFE    |

| 0            |              |

Figure 2: DIP Switch shows the DIP switch for the MXH932. It is used to configure the adapter card. Please leave all undocumented DIP switches in the default position. Table 4: DIP Switch settings shows all the various DIP switch settings for the MXH932.

#### **Figure 2: DIP Switch**

| DIP no. | Name      | Description                                                                                        | ON                                                      | OFF                                     | Default |

|---------|-----------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------|---------|

| 1-5     | OPT1-5    | Configuration selector, details below                                                              |                                                         |                                         | OFF     |

| 6       | OPT6      | Thermal Shutdown Disable.                                                                          | Will disable thermal shutdown                           | Card will shut down on thermal overheat | OFF     |

| 7       | MCU Reset | Holds the management processors<br>in reset. Do NOT ACTIVATE without<br>instructions from Dolphin. | Board management is<br>held in reset                    | Normal operation                        | OFF     |

| 8       | Reserved  | Do NOT ACTIVATE without instructions from Dolphin.                                                 | Do not activate without<br>instructions from<br>Dolphin | Normal operation                        | OFF     |

#### Table 4: DIP Switch settings

Note: DIP switch configuration options may be changed in future versions. Please always consult the latest version of the MXH932 User Guide for details. The table above is valid for BMC version 2.8.

#### **Thermal shutdown**

The MXH932 card includes an overtemperature overheat protection. The BMC will automatically shut down the MXH932 card if a PCIe switch temperature beyond 105°C (221°F) is detected. Similarly, if an AOC is plugged in, the MXH932 card will automatically shut down if the max operating temperature announced by the connected AOC is violated by 15°C (59°F). Please consult the AOC data sheet for details.

**NOTE:** The MXH932 link LEDs will start flashing yellow when a PCIe switch temperature of 95°C (203°F) is reached or when the AOC has reached the max operating temperature. Please consult the AOC data sheet for details.

**NOTE:** The automatic shutdown can be disabled by setting DIP-Switch OPT6. Prior to disabling the automatic shutdown, please ensure you have established proper airflow. Operating the card or AOC above the maximum specified operating temperature will void the warranty.

NOTE: If the card shuts down due to an overtemperature situation – you must improve the cooling before completely power cycling the system.

### **DIP switch Settings**

The following DIP Switch settings should be considered when configuring the MXH932 for Transparent Host operation:

**NOTE:** Revision Ax, Bx and Cx cards, prior to the volume production release shipped with default firmware version 1.0 to support a single x4, x8, or x16 link between two MXH932 cards. Please follow the instructions given in the MXH932 Firmware Release Note to upgrade the to the latest firmware to utilize transparent configurations.

#### **DIP Switch settings for MXH932 Host operation**

The following DIP Switch settings should be considered when configuring the MXH932 for Transparent Host operation:

| Use Case | Configuration MXH932 Host                   | DIP ON    | DIP switch view   |

|----------|---------------------------------------------|-----------|-------------------|

| A+D      | Transparent Host<br>One x16 downstream port | (all off) |                   |

|          | (P1+P2+P3+P4)                               | (Shipping | لكالكالكالكالكالك |

|          | Hot Plug Enabled                            | Default)  |                   |

| A+D      | Transparent Host<br>One x16 downstream port | OPT-4     |                   |

|          | (P1+P2+P3+P4)                               |           |                   |

|          | Hot Plug Disabled                           |           |                   |

| В        | Transparent Host<br>Two x8 downstream ports | OPT-1     |                   |

|          | (P1+P2, P3+P4)                              |           |                   |

|          | Hot Plug Enabled                            |           |                   |

| В        | Transparent Host                            | OPT-1     |                   |

|          | Two x8 downstream ports                     | OPT-4     |                   |

|          | (P1+P2, P3+P4)                              |           |                   |

|          | Hot Plug Disabled                           |           |                   |

| С        | Transparent Host                            | OPT-2     |                   |

|          | Four x4 downstream ports                    |           |                   |

|          | (P1, P2, P3, P4)                            |           |                   |

|          | Hot Plug Enabled                            |           |                   |

| С        | Transparent Host                            | OPT-2     |                   |

|          | Four x4 downstream ports                    | OPT-4     |                   |

|          | (P1, P2, P3, P4)<br>Hot Plug Disabled       |           |                   |

|          | Hot Plug Disabled                           |           |                   |

### **DIP Switch settings for MXH932 Target operation**

The following DIP Switch settings should be considered when configuring the **MXH932 for Transparent Target** operation:

| Use Case | Configuration MXH932 Target                                                                                                      | DIP ON         | DIP switch view |

|----------|----------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|

| A        | Transparent Target<br>One x4 - x16 upstream port<br>(P1+P2+P3+P4)<br>One x16 downstream port –<br>for use with e.g. IBP-G4X16-1  | OPT-1<br>OPT-2 |                 |

| F        | Transparent Target<br>One x4 - x16 upstream port<br>(P1+P2+P3+P4)<br>Dual x8 downstream ports –<br>for use with e.g. IBP-G4X16-3 | OPT 3          |                 |

| G        | Transparent Target<br>One x4 - x16 upstream port<br>(P1+P2+P3+P4)<br>Quad xx downstream ports–<br>for use with e.g. IBP-G4X16-5  | OPT 1<br>OPT 3 |                 |

### **Transparent Use Cases**

The MXH932 card may be used as both a Host card and a Target card. A Host and Target card can be used as a pair, or the Host card can be used with a PCI-SIG compliant Target device. The supported use cases and the DIP switch settings are summarized in section Configuration and DIP Switches on page 12.

#### **Target Card Clocking Option**

When the card is used in Transparent Target configuration, the default configuration settings will enable the card to provide a reference clock on the edge connector pins 13A + 14A.

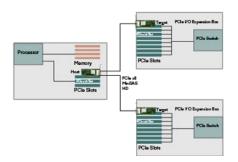

### Use Case A - 1 Host – Single Expansion Configuration PCIe x16

The Host system has an MXH932 adapter configured for Host operation and a direct x16 link to a MXH932 configured for Target operation. If you only need a x8 or x4 link, please configure according to use case B or C.

Figure 3: Use Case A

| Host card ports | Target card ports |

|-----------------|-------------------|

| P1              | P1                |

| P2              | P2                |

| P3              | P3                |

| P4              | P4                |

Table 5: Required x16 cabling

Always connect a cable from Port #x to Port #x

A failure connecting any of the cables will cause the link to re-train to x8 or x4.

#### Use Case B – 1 Host – Single or Dual Expansion Configuration – PCIe x8

The host has an MXH932 adapter configured for Transparent Host operation and a direct x8 link is used to connect one or two independent downstream target systems.

| Host card ports | Target card 1 ports | Target card 2 ports |

|-----------------|---------------------|---------------------|

| P1              | P1                  |                     |

| P2              | P2                  |                     |

| P3              |                     | P1                  |

| P4              |                     | P2                  |

Table 6: Required x8 cabling

#### Use Case C – 1 Host - Quad Expansion Configuration – PCIe x4

The host has an MXH932 adapter configured for Transparent Host operation and 1-4 direct x4 links is used to connect 1-4 independent downstream target systems.

Figure 4: Use Case C

| Host card ports | Target card 1 port | Target card 2 port | Target card 3 port | Target card 4 port |

|-----------------|--------------------|--------------------|--------------------|--------------------|

| P1              | P1                 |                    |                    |                    |

| P2              |                    | P1                 |                    |                    |

| P3              |                    |                    | P1                 |                    |

| P4              |                    |                    |                    | P1                 |

Table 7: Required x4 cabling

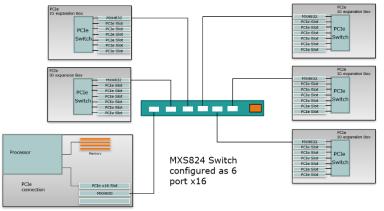

#### Use Case D – 1 Host – Transparent fan-out using MXS924 - PCle x16

The MXH932 is compliant with the MXS924 24 port PCIe switch. The switch enables large-scale Transparent PCIe fanout to hundreds of PCIe devices. Please find more details in the MXS924 Users Guide.

#### Use Case E – Multi Host – Transparent fan-out using MXS924 - PCIe x16

Please contact Dolphin for more information on how to configure the MXS924 and MXH932 for D-Switch mode. This configuration requires eXpressWare 5.20.0 or newer.

#### Use Case F – Transparent Target with two x8 Downstream ports

The MXH932 card with BMC firmware 2.8 supports splitting the downstream edge connector to support the IBP-G4X16-3 passive backplane and two x8 Plug-In adapter cards. Please consult the IBP-G4X16-3 Users Guide for more details.

### Use Case G – Transparent Target with four x4 Downstream ports

The MXH932 card with BMC firmware 2.8 supports splitting the downstream edge connector to support the IBP-G4X16-5 passive backplane and four x4 Plug-In adapter cards. Please consult the IBP-G4X16-5 Users Guide for more details.

### **EEPROM and Firmware Upgrade**

The MXH932 design uses a microcontroller to implement the PCIe CMI protocol and other maintenance functions. Dolphin may from time to time publish updated firmware for the Board Management Controller (BMC), PCIe switch or EEPROM data for the card.

**WARNING**: Please note that standard Microsemi tools (ChipLink) cannot be used to upgrade the firmware as this will violate the warranty. Please contact Dolphin for instructions on how to upgrade the MXH932 firmware.

Note: Please consult the MXH932 Firmware Release Note for details on supported configurations. The current BMC version is 2.8.

### **Identifying the Card**

The card has a label-sticker with the serial number in the format 'MXH932-YY-ZZZZZZ', where YY denotes the card revision (e.g. BB) and ZZZZZZ denotes the serialized production number (e.g. 012345) – this whole string makes up the serial number of the card (i.e. MXH932-BB-012345).

You can also get this information using lspci in Linux:

First, identify the devices for the Dolphin Host card:

# lspci | grep "Device 4036"

01:00.0 PCI bridge: PMC-Sierra Inc. Device 4036 01:00.1 Bridge: PMC-Sierra Inc. Device 4036 02:00.0 PCI bridge: PMC-Sierra Inc. Device 4036

Then run lspci and identify the card. It will show up as something like

| # lspci -s 1:0.0 -v                                                          |  |

|------------------------------------------------------------------------------|--|

| 01:00.0 PCI bridge: PMC-Sierra Inc. Device 4036 (prog-if 00 [Normal decode]) |  |

| Flags: bus master, fast devsel, latency 0, IRQ 122                           |  |

| Bus: primary=01, secondary=02, subordinate=03, sec-latency=0                 |  |

| I/O behind bridge: 00002000-00002fff                                         |  |

| Prefetchable memory behind bridge: 00000000c8000000-00000000c81fffff         |  |

| Capabilities: [40] Express Upstream Port, MSI 00                             |  |

| Capabilities: [7c] MSI: Enable+ Count=1/8 Maskable- 64bit+                   |  |

| Capabilities: [8c] Power Management version 3                                |  |

| Capabilities: [94] Subsystem: Dolphin Interconnect Solutions AS Device 0932  |  |

| Capabilities: [100] Advanced Error Reporting                                 |  |

| Capabilities: [148] Power Budgeting                                          |  |

| Capabilities: [158] #12                                                      |  |

| Capabilities: [188] #19                                                      |  |

| Capabilities: [1b4] Device Serial Number 00-00-43-43-00-00-00-24             |  |

| Capabilities: [1c0] Latency Tolerance Reporting                              |  |

| Capabilities: [1c8] Access Control Services                                  |  |

| Capabilities: [1f0] #25                                                      |  |

| Capabilities: [1fc] #26                                                      |  |

| Capabilities: [23c] #27                                                      |  |

| Capabilities: [7f8] Vendor Specific Information: ID=ffff Rev=1 Len=808       |  |

| Kernel driver in use: pcieport                                               |  |

| Kernel modules: shpchp                                                       |  |

Second, do

```

# lspci -s 1:0.0 -v | grep -E "Subsystem|Serial"

Capabilities: [a4] Subsystem: Dolphin Interconnect Solutions AS Device 0932

Capabilities: [100] Device Serial Number 00-00-42-42-00-00-00-ff

```

This shows the card as revision 0x4242 (hexadecimal values of the 'BB' letters in the ASCII table), with the production number 0x000000ff (00000255 in decimal).

# Support

More information about the product, support and software download can be found at <u>http://www.dolphinics.com/mx</u>. For general support questions, please contact Dolphin via the Jira Service Management portal: <u>https://www.dolphinics.com/csp</u>.

# **Technical Information**

### **Board revision history**

The following table gives a general overview of the hardware revision history. Please consult the MXH932 PCN available from Dolphin for details.

| Adapter card revision | Capabilities                                                 |

|-----------------------|--------------------------------------------------------------|

| MXH932-CC             | Initial product version                                      |

| MXH932-CE             | Adds support for AOC                                         |

| MXH932-DD             | New SFF-8644 connector due to EOL                            |

|                       | Replace PCIe oscillator with lower jitter variant (Si52254A) |

| MXH932-DE             | Replaced AOC current limiter due to long lead time           |

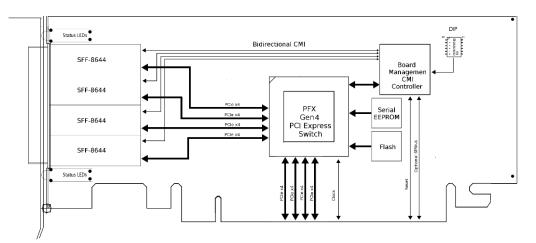

### **Simplified schematics**

The figure below shows the MXH932 simplified schematics. Only the main functions are shown.

Figure 5: MXH932 Simplified Schematics

### **PCIe Cable Port Signals**

The external PCI Express SFF-8644 cable connector supports the following signals:

- PETpN/PETnN: PCI Express Transmitter pairs, labeled where N is the Lane number (starting with 0); "p" is the true signal while "n" is the complement signal.

- PERpN/PERnN: PCI Express Receiver pairs, labeled where N is the Lane number (starting with 0); "p" is the true signal while "n" is the complement signal.

- PWR: Power to support AOC and signal conditioning components within the cable assembly.

- MGTPWR: Power supplied to the connector for cable management components that are needed while the link is not active. This needs to be active if the subsystem has power.

- CBLPRSNT#: Cable present detect, an active-low signal pulled-down by the cable when it is inserted into the MXH932 connector.

- CADDR: Signal used to configure the upstream cable management device address.

- CINT#: Signal asserted by the cable assembly to indicate a need for service via the CMI controller.

- CMISDA: Management interface data line. Used for both initial link setup and sideband messages when used with CMI compliant cables.

- CMISCL: Management interface clock line. Used for both initial link setup and sideband messages when used with CMI compliant cables.

### **External PCIe x4 Cable Connector Pin-Out**

|    |   |     |       |       |     | Column |       |     |           |        |

|----|---|-----|-------|-------|-----|--------|-------|-----|-----------|--------|

| Ro | w | 9   | 8     | 7     | 6   | 5      | 4     | 3   | 2         | 1      |

| D  |   | GND | PETn2 | PETp2 | GND | PETn1  | PETp1 | GND | MGTPWR    | PWR    |

| С  |   | GND | PETn3 | PETp3 | GND | PETn0  | PETp0 | GND | CMISDA    | CMISCL |

| В  |   | GND | PERn2 | PERp2 | GND | PERn1  | PERp1 | GND | CBLPRSNT# | PWR    |

| А  |   | GND | PERn3 | PERp3 | GND | PERn0  | PERp0 | GND | CINT#     | CADDR  |

|    |   | GND | _     | РЕКРЗ | -   | PERIIU | РЕКро | GND | CINT#     | CADDR  |

Table 8; External PCIe x4 cable Pin-Out

### **PCIe Cable Port Mapping**

The MXH932 card has a quad SFF-8644 connector. The table below show the signal / port map.

| Cable Port | x16 | Dual x8 | Quad x4 | PCle 3.0 Cable Pin |

|------------|-----|---------|---------|--------------------|

|            | L0  | L0      | L0      | TX0/RX0            |

| 1          | L1  | L1      | L1      | TX1/RX1            |

| I          | L2  | L2      | L2      | TX2/RX2            |

|            | L3  | L3      | L3      | TX3/RX3            |

|            | L4  | L4      | L0      | TX0/RX0            |

| 2          | L5  | L5      | L1      | TX1/RX1            |

| 2          | L6  | L6      | L2      | TX2/RX2            |

|            | L7  | L7      | L3      | TX3/RX3            |

|            | L8  | LO      | L0      | TX0/RX0            |

| 3          | L9  | L1      | L1      | TX1/RX1            |

| 5          | L10 | L2      | L2      | TX2/RX2            |

|            | L11 | L3      | L3      | TX3/RX3            |

|            | L12 | L4      | L0      | TX0/RX0            |

| 4          | L13 | L5      | L1      | TX1/RX1            |

| 4          | L14 | L6      | L2      | TX2/RX2            |

|            | L15 | L7      | L3      | TX3/RX3            |

|            |     |         |         |                    |

Lx – PCIe lane X, Cable port is ref PCIe bracket marking

Table 9 : PCIe Cable Port Mapping

# MXH932 PCIe x16 Edge Connector Pin-Out

The MXH932 Edge connector follows PCI Express CEM Specification, Rev. 4.0 section 6 – Card Connector Specification. Signal names are shown in Table 10. In host mode, the MXH932 is PCIe SIG compliant. The signals in **bold** are bi-directional, where the direction depends on if the card is configured for host or target mode. In the case where the MXH932 is configured as a target adapter in an expansion chassis, it will provide a 100 MHz, non-SSC, reference clock on the REFCLK+/REFCLK- pins. The shaded signals TDI and TDO are normally tri-stated but can be configured to provide an alternative 100 MHz, non-SSC, reference clock for PCIe expansion chassis utilizing these pins instead.

| Pin | Side B    | Note    | Side A  | Note          |

|-----|-----------|---------|---------|---------------|

| 1   | +12       |         | PRSNT1# |               |

| 2   | +12       |         | +12     |               |

| 3   | +12       |         | +12     |               |

| 4   | GND       |         | GND     |               |

| 5   | SMCLK     | BMC     | ТСК     | NC            |

| 6   | SMDAT     | BMC     | TDI     | O Ref clock   |

| 7   | GND       |         | TDO     | O Ref clock - |

| 8   | +3,3V     | PWR     | TMS     | NC            |

| 9   | TRST#     | NC      | +3,3    | PWR           |

| 10  | +3,3V aux | Standby | +3,3    | PWR           |

| 11  | WAKE#     | Wake up | PERST#  | Reset         |

| 12  |           | NC      | GND     |               |

| 13  | GND       |         | REFCLK+ | Ref clock +   |

| 14  | PERp0     | 1       | REFCLK- | Ref clock -   |

| 15  | PERn0     |         | GND     |               |

| 16  | GND       | 1       | PETp0   |               |

| 17  | PRSNT2#   |         | PETn0   |               |

| 18  | GND       |         | GND     |               |

| 19  | PERp1     |         |         | NC            |

| 20  | PERn1     |         | GND     |               |

| 21  | GND       |         | PETp1   |               |

| 22  | GND       |         | PETn1   |               |

| 23  | PERp2     |         | GND     |               |

| 24  | PERn2     |         | GND     |               |

| 25  | GND       |         | PETp2   |               |

| 26  | GND       |         | PETn2   |               |

| 27  | PERp3     |         | GND     |               |

| 28  | PERn3     |         | GND     |               |

| 29  | GND       |         | РЕТр3   |               |

| 30  |           | NC      | PETn3   |               |

| 31  | PRSNT2#   |         | GND     |               |

| 32  | GND       |         |         | NC            |

| 33  | PERp4     |         |         | NC            |

| 34  | PERn4     |         | GND     |               |

| 35  | GND       |         | PETp4   |               |

| 36  | GND       |         | PETn4   |               |

| 37  | PERp5     |         | GND     |               |

| 38  | PERn5     |         | GND     |               |

| 39  | GND       |         | PETp5   |               |

| 40  | GND       |         | PETn5   |               |

| 41  | PERp6     |         | GND     |               |

| 42  | PERn6     |         | GND     |               |

| 43  | GND       |         | PETp6   |               |

| 45       46       47       48       49       50       51       52       53       54       55       56 | GND<br>PERp7<br>PERn7<br>GND<br>PRSSNT2#<br>GND<br>PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND<br>GND |    | PETn6<br>GND<br>GND<br>PETp7<br>PETn7<br>GND<br>NC<br>GND<br>PETp8<br>PETn8<br>GND<br>GND<br>GND |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------|--|

| 46       47       48       49       50       51       52       53       54       55       56          | PERn7<br>GND<br>PRSSNT2#<br>GND<br>PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND<br>GND                 |    | GND<br>PETp7<br>PETn7<br>GND<br>NC<br>GND<br>PETp8<br>PETn8<br>GND                               |  |

| 47       48       49       50       51       52       53       54       55       56                   | GND<br>PRSSNT2#<br>GND<br>PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND<br>GND                          |    | PETp7<br>PETn7<br>GND<br>NC<br>GND<br>PETp8<br>PETn8<br>GND                                      |  |

| 48       49       50       51       52       53       54       55       56                            | PRSSNT2#<br>GND<br>PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND                                        |    | PETn7<br>GND<br>NC<br>GND<br>PETp8<br>PETn8<br>GND                                               |  |

| 49<br>50<br>51<br>52<br>53<br>54<br>55<br>56                                                          | GND<br>PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND                                                    |    | GND<br>NC<br>GND<br>PETp8<br>PETn8<br>GND                                                        |  |

| 50       51       52       53       54       55       56                                              | PERp8<br>PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND                                                           |    | NC<br>GND<br>PETp8<br>PETn8<br>GND                                                               |  |

| 51<br>52<br>53<br>54<br>55<br>56                                                                      | PERn8<br>GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND                                                                    |    | GND<br>PETp8<br>PETn8<br>GND                                                                     |  |

| 52<br>53<br>54<br>55<br>56                                                                            | GND<br>GND<br>PERp9<br>PERn9<br>GND<br>GND                                                                             |    | PETp8<br>PETn8<br>GND                                                                            |  |

| 53<br>54<br>55<br>56                                                                                  | GND<br>PERp9<br>PERn9<br>GND<br>GND                                                                                    |    | PETn8<br>GND                                                                                     |  |

| 54<br>55<br>56                                                                                        | PERp9<br>PERn9<br>GND<br>GND                                                                                           |    | GND                                                                                              |  |

| 55<br>56                                                                                              | PERn9<br>GND<br>GND                                                                                                    |    |                                                                                                  |  |

| 56                                                                                                    | GND<br>GND                                                                                                             |    | GND                                                                                              |  |

|                                                                                                       | GND                                                                                                                    |    |                                                                                                  |  |

| 57                                                                                                    |                                                                                                                        |    | PETp9                                                                                            |  |

|                                                                                                       |                                                                                                                        |    | PETn9                                                                                            |  |

| 58                                                                                                    | PERp10                                                                                                                 |    | GND                                                                                              |  |

| 59                                                                                                    | PERn10                                                                                                                 |    | GND                                                                                              |  |

| 60                                                                                                    | GND                                                                                                                    |    | PETp10                                                                                           |  |

| 61                                                                                                    | GND                                                                                                                    |    | PETn10                                                                                           |  |

| 62                                                                                                    | PERp11                                                                                                                 |    | GND                                                                                              |  |

| 63                                                                                                    | PERn11                                                                                                                 |    | GND                                                                                              |  |

| 64                                                                                                    | GND                                                                                                                    |    | PETp11                                                                                           |  |

| 65                                                                                                    | GND                                                                                                                    |    | PETn11                                                                                           |  |

| 66                                                                                                    | PERp12                                                                                                                 |    | GND                                                                                              |  |

| 67                                                                                                    | PERn12                                                                                                                 |    | GND                                                                                              |  |

| 68                                                                                                    | GND                                                                                                                    |    | PETp12                                                                                           |  |

| 69                                                                                                    | GND                                                                                                                    |    | PETn12                                                                                           |  |

| 70                                                                                                    | PERp13                                                                                                                 |    | GND                                                                                              |  |

| 71                                                                                                    | PERn13                                                                                                                 |    | GND                                                                                              |  |

| 72                                                                                                    | GND                                                                                                                    |    | PETp13                                                                                           |  |

| 73                                                                                                    | GND                                                                                                                    |    | PETn13                                                                                           |  |

| 74                                                                                                    | PERp14                                                                                                                 |    | GND                                                                                              |  |

| 75                                                                                                    | PERn14                                                                                                                 |    | GND                                                                                              |  |

| 76                                                                                                    | GND                                                                                                                    |    | PETp14                                                                                           |  |

| 77                                                                                                    | GND                                                                                                                    |    | PETn14                                                                                           |  |

| 78                                                                                                    | PERp15                                                                                                                 |    | GND                                                                                              |  |

| 79                                                                                                    | PERn15                                                                                                                 |    | GND                                                                                              |  |

| 80                                                                                                    | GND                                                                                                                    |    | PETp15                                                                                           |  |

| 81                                                                                                    | PRSNT2#                                                                                                                |    | PETn15                                                                                           |  |

| 82                                                                                                    |                                                                                                                        | NC | GND                                                                                              |  |

Table 10: PCIe Edge Connector Pin-Out

# **Compliance and Regulatory Testing**

#### EMC Compliance

The Dolphin PCI Express MXH932 adapter is tested to PASS the following relevant test standards for PCI Express cards, telecommunication and industry equipment installed in a standard PC:

- EN 55032:2012,

- EN 55035:2017,

- EN 61000-3-2:2014,

- EN 61000-3-3:2013

- 47 CFR Part 15, Subpart B (Clause 15.107 and 15.109) in conjunction with ANSI C63.4:2014

- CISPR 35:2016 Edition 1.0 (CISPR/I/412/CDV)

- Korean Harmonized standard, KN 35

This does not ensure that it will comply with these standards in any random PC. It is the responsibility of the integrator to ensure that their products are compliant with all regulations where their product will be used.

#### **RoHS Compliance**

The Dolphin MXH932 is RoHS compliant. A Compliance certificate issued by the manufacturer is available upon request.

### FCC Class A

This equipment is tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules.

### WEEE Notice

The adapter card is labelled in accordance with European Directive 2002/96/EC concerning waste electrical and electronic equipment (WEEE). The Directive determines the framework for the return and recycling of used appliances as applicable throughout the European Union. This label is applied to products to indicate that the product is not to be thrown away but returned to your local approved WEEE waste collector.

# **Limited Warranty**

Dolphin Interconnect Solutions warrants this product to be free from manufacturing defects under the following terms:

### **Warranty Period**

The warranty applies for one (1) year from the date of purchase. Extended warranty is available.

### Coverage

To the extent permitted by applicable law, this warranty does not apply to:

- Damage caused by operator error or non-compliance with instructions available for the product.

- Use or attempt to use or program firmware not approved by Dolphin.

- Damage due to accidents, abuse, misuse, improper handling or installation, moisture, corrosive environments, high voltage surges, shipping, or abnormal working conditions.

- Damage caused by acts of nature, e.g. floods, storms, fire, or earthquakes.

- Damage caused by any power source out of range or not provided with the product.

- Normal wear and tear.

- Attempts to repair, modify, open, or upgrade the product by personnel or agents not authorized by Dolphin.

- Products for which the serial number label has been tampered with or removed.

- Damage to the product caused by products not supplied by Dolphin.

### **Service Procedure**

In the event that the product proves defective during the Warranty Period, you should contact the seller that supplied you with the product, or if you purchased it directly from Dolphin, visit <u>https://www.dolphinics.com/csp</u> to obtain a valid RMA number and instructions. Products returned to Dolphin without a proper RMA number will not be serviced under this warranty.