# **Dolphin SG1010 Data Sheet**

**Revision Information:** 5.1

Copy Number: 000

#### January 2012

Dolphin, Inc. believes the information in this publication is correct; however, the information is subject to change without notice.

Dolphin, Inc. does not claim that the use of its products in the manner described in this publication will not infringe on any existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

©Dolphin, Inc. 2012. All rights reserved. Printed in U.S.A.

Dolphin, StarProtocol, StarFabric, and the Dolphin logo are trademarks of Dolphin, Inc.

All other trademarks and registered trademarks are the property of their respective owners.

# **Table of Contents**

### Introduction

| Featu | ures                                               |

|-------|----------------------------------------------------|

| 2.1   | Scalability and Performance                        |

| 2.2   | Compatibility                                      |

| 2.3   | Quality of Service                                 |

| 2.4   | Reliability, Availability, Serviceability features |

| 2.5   | Additional features                                |

| StarF | Fabric Features                                    |

| 3.1   | Scalability3-5                                     |

| 3.2   | Compenent Types                                    |

| 3.3   | Routing Methods                                    |

| 3.4   | Traffic Classes                                    |

| 3.5   | Fault Tolerant Strategies                          |

| 3.6   | Flow Control                                       |

| 3.7   | Bandwidth Reservation3-7                           |

| 3.8   | Usage Models                                       |

| Spec  | ifications                                         |

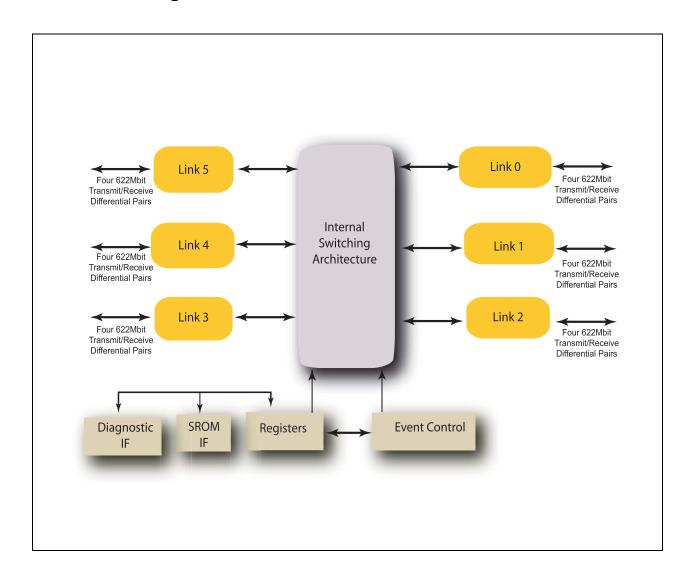

| 4.1   | Block Diagram                                      |

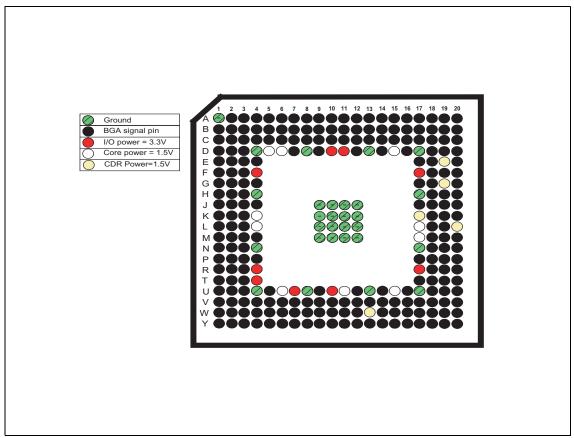

| 4.2   | Package Diagram4–10                                |

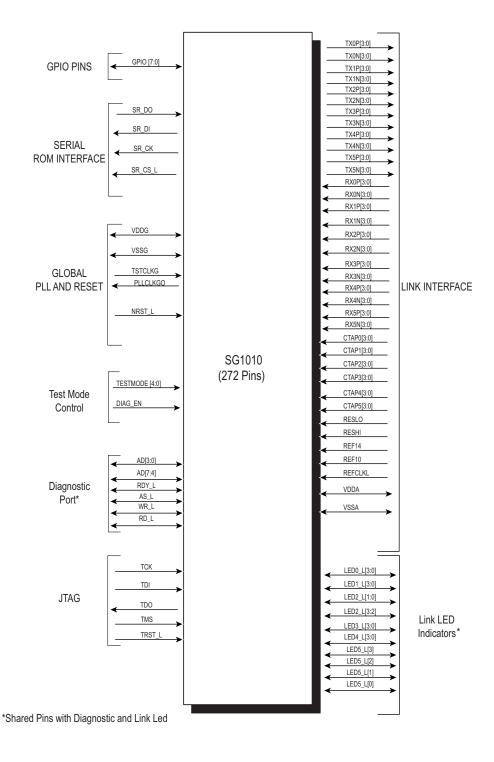

| 4.3   | Pinout Diagram4–11                                 |

| 4.4   | Pin List By Location                               |

| 4.5   | Power Pins4–17                                     |

| 4.6   | Pin Descriptions                                   |

| 4.7   | Package Specification                              |

| Elect | rical Specifications                               |

| 5.1   | Absolute Maximum Ratings                           |

| 5.2   | DC Specifications                                  |

| 5.3   | Timing Specifications           | 22 |

|-------|---------------------------------|----|

| 5.3.1 | Serial ROM Interface5-          | 22 |

| 5.3.2 | Global PLL Timing5–             | 22 |

| 5.3.3 | StarFabric Interface Timing     | 22 |

| 5.3.4 | Diagnostic Port Timing          | 23 |

| 5.3.5 | JTAG Timing5–                   | 24 |

| 5.3.6 | Asynchronous and Static Signals | 24 |

| Cont  | act Information                 |    |

| 6.1   | Headquarters 6-                 | 25 |

2 January 17, 2012

# Introduction

The Dolphin SG1010 GDolphin Switch facilitates the design of high-performance and reliable StarFabric based switching systems. System designers can develop high performance systems that deliver voice, video, and data. A single-chip solution, the SG1010 offers six 2.5Gbps full duplex serial links, which deliver 30Gbps of aggregate, non-blocking, full duplex switching capacity.

Along with its high performance, the SG1010 can handle content-rich traffic through its extensive functionality and Quality of Service (QOS) support. The SG1010 supports 4 classes of service along with three routing methods providing added flexibility. The SG1010 is designed to work with other StarFabric devices and supports bridge products that employ protocols such as PCI and H.110. System designers can build system architectures that easily combine control, voice, cell and packet data.

The SG1010 allows PCI based designs to be easily migrated to StarFabric, yet maintain their investments in software and applications. The SG1010 supports two addressing models – a StarFabric address model and a PCI address model. In the StarFabric address model, the SG1010 switches path-routed and multicast frames. To support the PCI address model, the SG1010 appears as a PCI-to-PCI bridge to PCI configuration software. The SG1010 includes a PCI-compliant type1 header for 100% compatibility with existing PCI BIOS, drivers, application SW, and operating systems.

Designers don't have to deal with significant physical interface issues, which minimizes time-to-market. The SG1010 utilizes 622Mbps low voltage differential signaling (LVDS), a technology that is widely applied and thoroughly understood by industry professionals. Four transmit and receive differential pairs create a single 2.5Gbps full duplex link with 5Gbps of total bandwidth. StarFabric designs can span from chip-to-chip to room area networks. Inexpensive twisted pair copper cable can yield distances greater than 10 meters.

The SG1010 allows system designers to cost effectively engineer highly reliable and available systems. SG1010 system designs can include redundant data paths, so if a particular path fails, traffic can be rerouted over an alternate path. The SG1010 supports detection and notification of link status changes, as well as Hot-pluggable links. Path notification messages alerts operations personnel to replace faulty components and through hot swap, the offending boards can be replaced without affecting the rest of the

January 17, 2012 Introduction 1–1

system. The 2.5 Gbps links also tolerate failure of up to three of the four differential pairs in a link. The re-striping of data is done automatically in silicon when differential pairs fail.

By combining the SG1010 with other StarFabric Devices, new multi-protocol, highly reliable, high performance systems can be acheived. The SG1010 offers a comprehensive solution, which includes silicon, software, and platforms to help achieve faster time-to- market.

**1–2** Introduction January 17, 2012

2

# **Features**

### 2.1 Scalability and Performance

- 6 fabric links, 2.5 Gbps, full duplex

- 30 Gbps switching capacity

- Design limits head-of-line blocking

- Credit-based flow control

#### 2.2 Compatibility

- Support for routing methods including PC compatible address routing

- Flexible Addressing Capability

- Physical layer interface is compliant with the IEEE 1596.3 and TIA/EIA-644 Low-Voltage Differential Signaling (LVDS) standards.

### 2.3 Quality of Service

- Specific credits for next-turn and class-of-service

- Separate buffering for Asynchronous, Isochronous, Multicast, and High Priority traffic classes.

- Path routing

- Multicast routing

- Dynamic bandwidth reservation protocol

### 2.4 Reliability, Availability, Serviceability features

- Link-by-link CRC checking on all traffic

- Redundant path routing capability

- Hot-pluggable links

#### 2.5 Additional features

• IEEE standard 1149.1 JTAG interface

January 17, 2012 Features 2–3

Additional features Copy 000

- Eight general-purpose I/O pins with accessible registers

- LED indicators for each differential pair

**2–4** Features January 17, 2012

3

# **StarFabric Features**

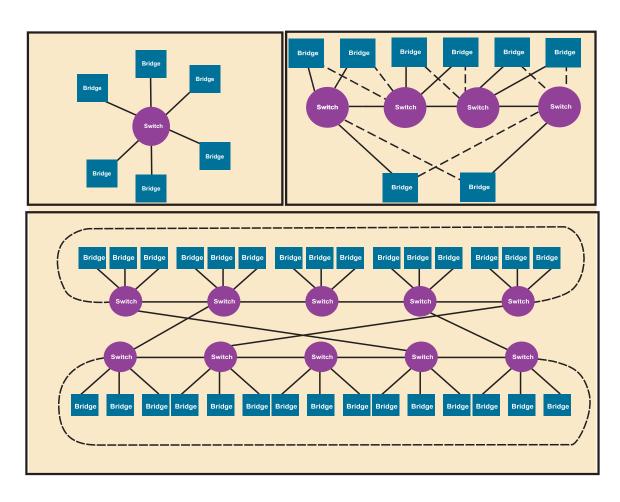

### 3.1 Scalability

The SG1010 switch has 30Gbps of switching capacity. When cascaded, the device enables systems to scale to gigabytes per second of capacity. The initial physical layer implemented provides 2.5 Gbps full-duplex bandwidth per link. Two links can be aggregated to create a 'fat pipe' with double the bandwidth. The links are well suited for chip-to-chip, backplane, and rack-to-rack interconnect. Using standard category 5 unshielded copper cables the links can extend to over 10 meters in length enabling the creation of room scale equipment.

January 17, 2012 StarFabric Features 3–5

#### 3.2 Compenent Types

The two component types in StarFabric are edge nodes and switches. Swithes forward traffic through the StarFabric. Edge nodes provide the connection between the fabric and other protocols or devices. Bridges are edge nodes that translate other protocols (e.g., PCI, H.110) into serial StarFabric traffic. An edge node is further classified into either a root or a leaf. The root initiates fabric resets and enumeration.

### 3.3 Routing Methods

- Address Routing

- Provides full compatibility with standards like PCI, Path and Multicast routing

- Path and Multicast routing

- Provides Quality of service, reliability, and high availability

#### 3.4 Traffic Classes

StarFabric supports 7 traffic classes. The initial parts support 4 traffic classes.

- Asynchronous / address routed class

- Isochronous Class

- Multicast Class

- High Priority Class

### 3.5 Fault Tolerant Strategies

- Parallel Fabrics

- A second fabric provides redundancy. Redundant switches are used so that any switch may fail, yet end nodes remain connected. If a particular path fails, packets can be re-routed by silicon or software over the remaining functional paths.

- Fragile links

- Automatic re stripping of data over functioning differential pairs in a link when one to three pairs fail.

#### 3.6 Flow Control

Line credits manage flow control. Line credits are counters used to track available buffer storage between link partners. Each transmission point in the fabric has buffers for each class of traffic for each outgoing port. Traffic is sent only when the source has line credits for the output buffer on the next node for an entire frame. A switch is non-blocking because edge node congestion does not impact traffic flow to any other edge node or even to the same edge node in a different class of service. Line credits are used when a node sends a frame and restored when the node's link partner forwards the frame.

**3–6** StarFabric Features January 17, 2012

#### 3.7 Bandwidth Reservation

Isochronous and multicast transmissions can use bandwidth reservation to allocate anticipated bandwidth requirements prior to starting data transfer. Bandwidth reservation is fully distributed and is initiated at the origin of the traffic.

#### 3.8 Usage Models

Current StarFabric components support 3 usage models, PCI legacy, Fabric-native, and mixed legacy / Fabric-native. PCI legacy enables use of existing PCI drivers and initialization software with no modification. the interconnect looks like a collection of PCI-to-PCI bridges. This usage model amounts to a plug-and-play mode that extends the capabilities of existing systems.

The Fabric-native usage unleashes some of the StarFabric's advanced features such as path routing, class of service, bandwidth selection, redundancy for fail-over path routing, and channels. Fabric-native use also provides the isolation and mechanisms required for inter-processor communication. This enables distributed computing applications. It is possible to use a mixture of legacy and fabric-native capabilities. Developers can start with legacy and add enhanced fabric- native capability over time.

To use advanced features, some degree of software investment is necessary. Dolphin provides software tools to take advantage of StarFabric's advanced features. Sample software includes enumeration and routing, bandwidth reservation, as well as routines for optimizing performance, API integration layers, BIOS/initial setup, and generating statistics. DolphinDolphin supplies tools and utilites for ROM programming, fabric access tools, and Fabric topology viewers.

January 17, 2012 StarFabric Features 3–7

Usage Models Copy 000

**3–8** StarFabric Features January 17, 2012

### 4.1 Block Diagram

Package Diagram Copy 000

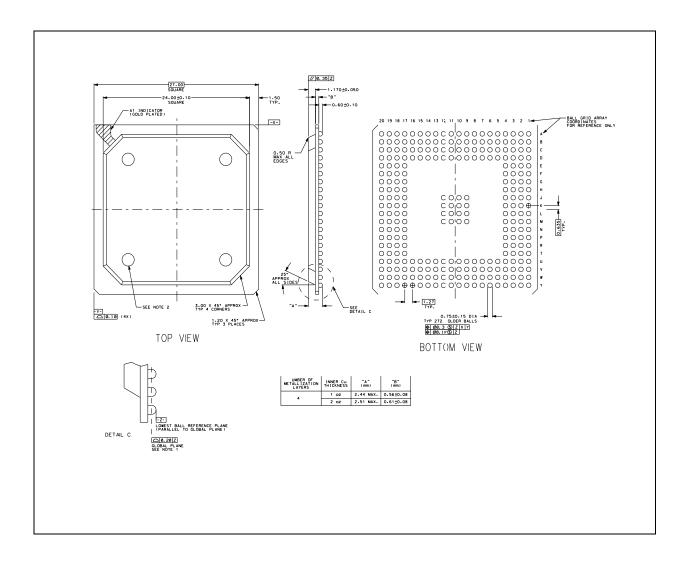

### 4.2 Package Diagram

Figure 4-1 Top View Package Diagram

4–10 Specifications January 17, 2012

Copy 000 Pinout Diagram

### 4.3 Pinout Diagram

# 4.4 Pin List By Location

Table 4-1 Pin by Location

| Pin | Signal Name  | Туре |

|-----|--------------|------|

| B1  | tx1p[0]      | 0    |

| C2  | tx1n[0]      | 0    |

| D2  | tx1p[1]      | 0    |

| D3  | tx1n[1]      | 0    |

| E4  | tx1p[2]      | 0    |

| E3  | tx1n[2]      | 0    |

| D1  | tx1p[3]      | 0    |

| C1  | tx1n[3]      | 0    |

| E2  | tx0p[0]      | 0    |

| E1  | tx0n[0]      | 0    |

| F3  | tx0p[1]      | 0    |

| G4  | tx0n[1]      | 0    |

| F2  | tx0p[2]      | 0    |

| F1  | tx0n[2]      | 0    |

| G3  | tx0p[3]      | 0    |

| G2  | tx0n[3]      | 0    |

| G1  | tx5p[0]      | 0    |

| Н3  | tx5n[0]      | 0    |

| H2  | tx5p[1]      | 0    |

| H1  | tx5n[1]      | 0    |

| J4  | tx5p[2]      | 0    |

| J3  | tx5n[2]      | 0    |

| J2  | tx5p[3]      | 0    |

| J1  | tx5n[3]      | 0    |

| K2  | reserved[0]  | IO   |

| K3  | reserved[1]  | IO   |

| K1  | reserved[2]  | IO   |

| L1  | reserved[3]  | IO   |

| L2  | reserved[4]  | IO   |

| L3  | reserved[5]  | IO   |

| M1  | reserved[6]  | IO   |

| M2  | reserved[7]  | IO   |

| M3  | reserved[8]  | IO   |

| M4  | reserved[9]  | IO   |

| N1  | reserved[10] | IO   |

| N2  | reserved[11] | IO   |

**4–12** Specifications January 17, 2012

Table 4-1 Pin by Location

| Pin | Signal Name  | Туре |

|-----|--------------|------|

| N3  | reserved[12] | IO   |

| P1  | reserved[13] | IO   |

| P2  | reserved[14] | IO   |

| R1  | reserved[15] | IO   |

| P3  | reserved[16] | IO   |

| R2  | reserved[17] | IO   |

| T1  | reserved[18] | IO   |

| P4  | diag_en      | I    |

| R3  | testmode[4]  | I    |

| T2  | tck          | I    |

| U1  | trst_1       | I    |

| Т3  | tms          | I    |

| U2  | tdo          | 0    |

| V1  | tdi          | I    |

| U3  | scan_ena     | I    |

| V2  | spare        | I    |

| W1  | scan_out[0]  | IO   |

| V3  | scan_out[1]  | IO   |

| W2  | scan_out[2]  | IO   |

| Y1  | scan_out[3]  | IO   |

| W3  | scan_out[4]  | IO   |

| Y2  | scan_out[5]  | IO   |

| W4  | scan_out[6]  | IO   |

| V4  | scan_out[7]  | IO   |

| U5  | testmode[3]  | I    |

| Y3  | testmode[2]  | I    |

| Y4  | testmode[1]  | I    |

| V5  | testmode[0]  | I    |

| W5  | sr_cs_1      | IO   |

| Y5  | sr_ck        | IO   |

| V6  | sr_di        | IO   |

| W6  | sr_do        | I    |

| Y6  | gpio[7]      | IO   |

| V7  | gpio[6]      | IO   |

| W7  | gpio[5]      | IO   |

| Y7  | gpio[4]      | IO   |

| V8  | gpio[3]      | IO   |

| W8  | gpio[2]      | IO   |

Table 4-1 Pin by Location

| Pin | Signal Name | Туре |

|-----|-------------|------|

| Y8  | gpio[1]     | IO   |

| U9  | gpio[0]     | IO   |

| V9  | nrst_1      | I    |

| W9  | tstclkg     | I    |

| Y9  | pllclkgo    | 0    |

| W10 | led5_l[3]   | IO   |

| V10 | led5_l[2]   | IO   |

| Y10 | led5_l[1]   | IO   |

| Y11 | led5_l[0]   | IO   |

| W11 | led4_1[3]   | IO   |

| V11 | led4_1[2]   | IO   |

| Y12 | led4_1[1]   | IO   |

| W12 | led4_1[0]   | IO   |

| V12 | led3_1[3]   | IO   |

| U12 | led3_1[2]   | IO   |

| Y13 | led3_l[1]   | IO   |

| Y14 | led3_l[0]   | IO   |

| W14 | led2_1[3]   | IO   |

| Y15 | led2_1[2]   | IO   |

| V14 | led2_l[1]   | IO   |

| W15 | led2_l[0]   | IO   |

| Y16 | led1_1[3]   | IO   |

| U14 | led1_1[2]   | IO   |

| V15 | led1_l[1]   | IO   |

| W16 | led1_l[0]   | IO   |

| Y17 | led0_1[3]   | IO   |

| V16 | led0_1[2]   | IO   |

| W17 | led0_1[1]   | IO   |

| Y18 | led0_1[0]   | IO   |

| U16 | tstshftld   | I    |

| V17 | ecsel       | I    |

| W18 | etoggle     | I    |

| Y19 | exdnup      | I    |

| V18 | tstphase    | I    |

| W19 | resettx     | I    |

| Y20 | loopbken    | I    |

| W20 | testrst     | I    |

| V19 | bypassl     | I    |

**4–14** Specifications January 17, 2012

Table 4-1 Pin by Location

| Pin | Signal Name | Туре |

|-----|-------------|------|

| U19 | tstclkl     | I    |

| U18 | refclkl     | I    |

| T17 | ctap5[0]    | I    |

| V20 | rx5p[0]     | I    |

| U20 | rx5n[0]     | I    |

| T18 | rx5p[1]     | I    |

| T19 | rx5n[1]     | I    |

| T20 | ctap5[1]    | I    |

| R18 | rx5p[2]     | I    |

| P17 | rx5n[2]     | I    |

| R19 | ctap5[2]    | I    |

| R20 | ctap5[3]    | I    |

| P18 | rx5p[3]     | I    |

| P19 | rx5n[3]     | I    |

| P20 | ctap0[0]    | I    |

| N18 | rx0p[0]     | I    |

| N19 | rx0n[0]     | I    |

| N20 | ctap0[1]    | I    |

| M18 | rx0p[1]     | I    |

| M19 | rx0n[1]     | I    |

| M20 | rx0p[2]     | I    |

| L19 | rx0n[2]     | I    |

| L18 | ctap0[2]    | I    |

| K19 | rx0p[3]     | I    |

| K18 | rx0n[3]     | I    |

| J19 | ctap0[3]    | I    |

| J18 | rx1p[0]     | I    |

| J17 | rx1n[0]     | I    |

| H20 | ctap1[0]    | I    |

| H19 | rx1p[1]     | I    |

| H18 | rx1n[1]     | I    |

| G20 | ctap1[1]    | I    |

| G18 | rx1p[2]     | I    |

| F19 | rx1n[2]     | I    |

| E20 | ctap1[2]    | I    |

| G17 | rx1p[3]     | I    |

| F18 | rx1n[3]     | I    |

| E18 | ctap1[3]    | I    |

Table 4-1 Pin by Location

| Pin | Signal Name | Туре |

|-----|-------------|------|

| D19 | rx2p[0]     | I    |

| C20 | rx2n[0]     | I    |

| E17 | ctap2[0]    | I    |

| D18 | rx2p[1]     | I    |

| C19 | rx2n[1]     | I    |

| B20 | ctap2[1]    | I    |

| C18 | rx2p[2]     | I    |

| B19 | rx2n[2]     | I    |

| A20 | ctap2[2]    | I    |

| A19 | rx2p[3]     | I    |

| B18 | rx2n[3]     | I    |

| B17 | ctap2[3]    | I    |

| C17 | rx3p[0]     | I    |

| D16 | rx3n[0]     | I    |

| A18 | ctap3[0]    | I    |

| A17 | rx3p[1]     | I    |

| C16 | rx3n[1]     | I    |

| B16 | ctap3[1]    | I    |

| A16 | ctap3[2]    | I    |

| C15 | rx3p[2]     | I    |

| D14 | rx3n[2]     | I    |

| B15 | rx3p[3]     | I    |

| A15 | rx3n[3]     | I    |

| C14 | ctap3[3]    | I    |

| B14 | rx4p[0]     | I    |

| A14 | rx4n[0]     | I    |

| C13 | ctap4[0]    | I    |

| B13 | rx4p[1]     | I    |

| A13 | rx4n[1]     | I    |

| D12 | ctap4[1]    | I    |

| C12 | rx4p[2]     | I    |

| B12 | rx4n[2]     | I    |

| A12 | ctap4[2]    | I    |

| B11 | rx4p[3]     | I    |

| C11 | rx4n[3]     | I    |

| A11 | ctap4[3]    | I    |

| A10 | tx4p[0]     | 0    |

| B10 | tx4n[0]     | 0    |

**4–16** Specifications January 17, 2012

Copy 000 Power Pins

Table 4-1 Pin by Location

| Pin | Signal Name | Туре |

|-----|-------------|------|

| C10 | tx4p[1]     | 0    |

| C9  | tx4n[1]     | 0    |

| B9  | tx4p[2]     | 0    |

| A9  | tx4n[2]     | 0    |

| D9  | tx4p[3]     | 0    |

| C8  | tx4n[3]     | 0    |

| B8  | tx3p[0]     | 0    |

| A8  | tx3n[0]     | 0    |

| A7  | tx3p[1]     | 0    |

| B7  | tx3n[1]     | 0    |

| B6  | tx3p[2]     | 0    |

| C7  | tx3n[2]     | 0    |

| A6  | tx3p[3]     | 0    |

| A5  | tx3n[3]     | 0    |

| D7  | tx2p[0]     | 0    |

| C6  | tx2n[0]     | 0    |

| B5  | tx2p[1]     | 0    |

| A4  | tx2n[1]     | 0    |

| C5  | tx2p[2]     | 0    |

| B4  | tx2n[2]     | 0    |

| A3  | tx2p[3]     | 0    |

| B3  | tx2n[3]     | 0    |

| C4  | reslo       | I    |

| B2  | reshi       | I    |

| A2  | ref14       | I    |

| C3  | ref10       | I    |

# 4.5 Power Pins

Table 4–2 Power Pins

| Description | Pins                                                                                                 |

|-------------|------------------------------------------------------------------------------------------------------|

| Ground      | A1,D4,D8,D13,D17,H4,H17,J9,J10,J11,J12,K9,K10,K11,K12,L9,L11,L12,M9,M10,M11,M12,N4,N17,U4,U8,U13,U17 |

| Vdd 3.3V    | D11,F4,F17,R4,R17,U10,D10,T4,U7                                                                      |

| Vdd 1.5V    | D6,D15,K4,L17,U6,U15,D5,L4,M17,U11                                                                   |

| Analog 1.5V | L20,G19,K17,E19,W13                                                                                  |

| Vssa        | V13,K20,J20,D20,F20                                                                                  |

Pin Descriptions Copy 000

# 4.6 Pin Descriptions

Table 4-3 Pin Descriptions

| Pin       | Description                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|

| SR_DO     | SROM data out. Receives read data from the Serial Rom.                                                                      |

| SR_DI     | SROM data in. The SG1010 drives the SROM command, address, and write data on this signal                                    |

| SR_CK     | SROM clock input.                                                                                                           |

| SR_CS_L   | SROM chip select. The SG1010 drives this signal low at the beginning of an SROM operation; high at the end of the operation |

| VDDG      | VDD for 112.5MHz phase-locked loop (PLL)                                                                                    |

| VSSG      | VSS for 112.5MHz PLL                                                                                                        |

| TSTCLKG   | Bypass clock for 112.5 MHz PLL. Bypass mode is selected through TESTMODE [4:0] pins                                         |

| PLLCLKGO  | 112.5MHz PLL output (used for test)                                                                                         |

| NRST_L    | Chip reset pin                                                                                                              |

| TX0P[3:0] | Link 0 LVDS transmit positive                                                                                               |

| TX0N[3:0] | Link 0 LVDS transmit negative                                                                                               |

| TX1P[3:0] | Link 1 LVDS transmit positive                                                                                               |

| TX1N[3:0] | Link 1 LVDS transmit negative                                                                                               |

| TX2P[3:0] | Link 2 LVDS transmit positive                                                                                               |

| TX2N[3:0] | Link 2 LVDS transmit negative                                                                                               |

| TX3P[3:0] | Link 3 LVDS transmit positive                                                                                               |

| TX3N[3:0] | Link 3 LVDS transmit negative                                                                                               |

| TX4P[3:0] | Link 4 LVDS transmit positive                                                                                               |

| TX4N[3:0] | Link 4 LVDS transmit negative                                                                                               |

| TX5P[3:0] | Link 5 LVDS transmit positive                                                                                               |

| TX5N[3:0] | Link 5 LVDS transmit negative                                                                                               |

| RX0P[3:0] | Link 0 LVDS receive positive                                                                                                |

| RX0N[3:0] | Link O LVDS receive negative                                                                                                |

| RX1P[3:0] | Link 1 LVDS receive positive                                                                                                |

| RX1N[3:0] | Link 1 LVDS receive negative                                                                                                |

| RX2P[3:0] | Link 2 LVDS receive positive                                                                                                |

| RX2N[3:0] | Link 2 LVDS receive negative                                                                                                |

| RX3P[3:0] | Link 3 LVDS receive positive                                                                                                |

| RX3N[3:0] | Link 3 LVDS receive negative                                                                                                |

| RX4P[3:0] | Link 4 LVDS receive positive                                                                                                |

| RX4N[3:0] | Link 4 LVDS receive negative                                                                                                |

| RX5P[3:0] | Link 5 LVDS receive positive                                                                                                |

| RX5N[3:0] | Link 5 LVDS receive negative                                                                                                |

| REFCLKL   | Reference clock for CDR PLL                                                                                                 |

**4–18** Specifications January 17, 2012

Copy 000 Pin Descriptions

Table 4-3 Pin Descriptions

| Pin           | Description                                                               |

|---------------|---------------------------------------------------------------------------|

| CTAP0[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| CTAP1[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| CTAP2[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| CTAP3[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| CTAP4[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| CTAP5[3:0]    | Link 5 LVDS center taps for external reference voltages                   |

| RESLO         | LVDS 100OHM reference low- connects to RESHI through 100OHM 1% resistor   |

| RESHI         | LVDS 100OHM reference high- connects to RESLO through 100 OHM 1% resistor |

| REF14         | LVDS 1.4V reference                                                       |

| REF10         | LVDS 1.0V reference                                                       |

| VDDA          | Analog VDD for CDR PLL                                                    |

| VSSA          | Analog VSS for CDR PLL                                                    |

| TSTCLKL       | Manufacturing Test Pin                                                    |

| BYPASSL       | Manufacturing Test Pin                                                    |

| RESETTX       | Manufacturing Test Pin                                                    |

| TESTRST       | Manufacturing Test Pin                                                    |

| TSTSHFTLD     | Manufacturing Test Pin                                                    |

| ECSEL         | Manufacturing Test Pin                                                    |

| ETOGGLE       | Manufacturing Test Pin                                                    |

| EXDNUP        | Manufacturing Test Pin                                                    |

| TSTPHASE      | Manufacturing Test Pin                                                    |

| LOOPBKEN      | Manufacturing Test Pin                                                    |

| TESTMODE[4:0] | Enables SG1010 functional/test                                            |

| DIAG_EN       | Diagnostic Port Enable                                                    |

| LED0_L[3:0]   | Transmit state LEDs for link0                                             |

| LED1_L[3:0]   | Transmit state LEDs for link1                                             |

| LED2_L[3:0]   | Transmit state LEDs for link2                                             |

| LED3_L[3:0]   | Link 3 state LEDs                                                         |

| LED4_L[3:0]   | Link 4 state LEDs                                                         |

| LED5_L[3:0]   | Link 5 state LEDs                                                         |

| TCK           | JTAG clock                                                                |

| TDI           | JTAG data in                                                              |

| TDO           | JTAG data out                                                             |

| TMS           | JTAG mode select                                                          |

| TRST_L        | JTAG reset                                                                |

| SCAN_ENA      | Scan enable input                                                         |

| SCAN_OUT[7:0] | Scan chain outputs                                                        |

|               |                                                                           |

Table 4-3 Pin Descriptions

| Pin     | Description                                    |

|---------|------------------------------------------------|

| AD[7:0] | Diagnostic port AD[7:0]                        |

| RDY_L   | Diagnostic Port Control Signal: Target Ready   |

| AS_L    | Diagnostic Port Control Signal: Address Strobe |

| WR_L    | Diagnostic Port Control Signal: Write strobe   |

| RD_L    | Diagnostic Port Control Signal: read strobe    |

### 4.7 Package Specification

**4–20** Specifications January 17, 2012

# **Electrical Specifications**

### 5.1 Absolute Maximum Ratings

Table 5-1 Ratings

| Max Junction Temperature          | 125 degrees C             |

|-----------------------------------|---------------------------|

| Core Supply Voltage               | 1.5V +/-5%                |

| I/O Supply Voltage                | 3.3V +/-5%                |

| Storage Temperature               | -55 to 125 degrees C      |

| Operating Temperature             | -40C to Max Junction Temp |

| Theta-Jb                          | 12.0C/W                   |

| Theta-Jc                          | 6.0C/W                    |

| Theta-Ja                          | 20.6 C/W                  |

| Theta-Jma at 1.0 m/s(~200 ft/min) | 16.1 C/W                  |

| Theta-Jma at 2.5 m/s(~500Ft/min)  | 14.4 C/W                  |

| Power dissipation                 | 3W maximum                |

### 5.2 DC Specifications

Table 5-2 DC Specifications (non-LVDS signals)

| Symbol              | Parameter             | Condition                 | Min               | Max                    |

|---------------------|-----------------------|---------------------------|-------------------|------------------------|

| V <sub>ih</sub>     | Input high voltage    | _                         | .5V <sub>cc</sub> | .5V <sub>cc</sub> +.5V |

| V <sub>il</sub>     | Input low voltage     | _                         | -0.5V             | $.3V_{cc}$             |

| $V_{ipu}$           | Input Pull-up voltage | _                         | .7V <sub>cc</sub> | _                      |

| V <sub>oh</sub>     | Output high voltage   | $I_{oh} = -500 \text{mA}$ | .9V <sub>cc</sub> | _                      |

| $V_{ol}$            | Output low voltage    | $I_{ol} = 1500 \text{mA}$ | _                 | $.1V_{cc}$             |

| I <sub>in</sub>     | Input leakage current | $0 \le V_{in} \le V_{io}$ | _                 | <u>+</u> 10 μA         |

| I <sub>in-pme</sub> | PME_L input leakage   | $V_o \le 3.6V$            | _                 | -1 mA                  |

|                     |                       | $V_{cc}$ off              |                   |                        |

| C <sub>in</sub>     | Pin capacitance       | _                         | _                 | 10 pF                  |

### 5.3 Timing Specifications

#### 5.3.1 Serial ROM Interface

Table 5–3 Serial ROM Interface AC Timing Specifications

| Signal  | Symbol               | Parameter                  | Min                    | Max |

|---------|----------------------|----------------------------|------------------------|-----|

| SR_CLK  | T <sub>scyc</sub>    | Cycle time                 | 510ns                  | _   |

| SR_CS_L | $T_{scsl}$           | Minimum time low           | 56.5*T <sub>scyc</sub> | -   |

| SR_CS_L | T <sub>scssu</sub>   | Setup to SR_CLK rising     | .5*T <sub>scyc</sub>   | -   |

| SR_DO   | $T_{sdosu}$          | Setup to SR_CLK rising     | 30ns                   | _   |

| SR_DO   | $T_{sdoh}$           | Hold from SR_CLK rising    | 30ns                   | _   |

| SR_DI   | T <sub>sdivalb</sub> | Valid before SR_CLK rising | .5*T <sub>scyc</sub>   | _   |

| SR_DI   | $T_{sdivala}$        | Valid from SR_CLK rising   | .5*T <sub>scyc</sub>   | _   |

#### 5.3.2 Global PLL Timing

Table 5-4 Global PLL and Reset AC Timing Specifications

| Signal  | Symbol              | Parameter                                 | Min                  | Max                  |

|---------|---------------------|-------------------------------------------|----------------------|----------------------|

| REFCLKL | F <sub>xtal</sub>   | Frequency                                 | 62.208MHz<br>- 20ppm | 62.208MHz<br>+ 20ppm |

| REFCLKL | V <sub>refptp</sub> | Peak-to-peak voltage                      |                      |                      |

| REFCLKL |                     | Slew rate                                 | X V/ns               | Y V/ns               |

| REFCLKC |                     | Duty Cycle                                |                      |                      |

| NRST_L  | T <sub>rstv</sub>   | Minimum assertion time after power stable | 10μσεχ               |                      |

#### 5.3.3 StarFabric Interface Timing

Table 5-5 LVDS StarFabric Interface AC Timing Specifications

| Signal                 | Symbol        | Parameter         | Min   | Max   |

|------------------------|---------------|-------------------|-------|-------|

| TXnP, TXnN             | $T_{tdpsk}$   | Differential skew |       | 50ps  |

| TXnP, TXnN             | $T_{tppsk}$   | Pair to pair skew |       | 200ps |

| TXnP, TXnN             | $T_{tdpr}(2)$ | Low to high time  | 100ps | 210ps |

| TXnP, TXnN             | $T_{tdpf}(2)$ | High to low time  | 100ps | 210ps |

| RXnP, RXnN             | $T_{rdpsk}$   | Differential skew |       |       |

| RXnP, RXnN             | $T_{rppsk}$   | Pair to pair skew |       | 2ns   |

| RXnP, RXnN             | $T_{rdpr}$    | Low to high time  |       |       |

| RXnP, RXnN             | $T_{rdpf}$    | High to low time  |       |       |

| TXnP, TXnN, RXnP, RXnN | $T_{dpfreq}$  | Maximum frequency |       |       |

(2) Test conditions: ZL=100O±1%, Cpad=3.0pF, Cpadn=3.0pF

#### 5.3.4 Diagnostic Port Timing

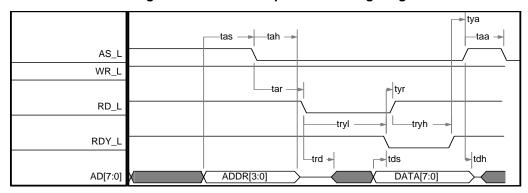

Table 5-6 Diagnostic Port Read Operation Timing Diagram

Table 5-7 Diagnostic Port Read Operation AC Timing

| Signal  | Symbol           | Parameter                          | Min  | Max      |

|---------|------------------|------------------------------------|------|----------|

| AD[3:0] | t <sub>as</sub>  | Setup time to AS_L asserted        | 13ns | _        |

| AD[3:0] | t <sub>ah</sub>  | Hold time from AS_L asserted       | 23ns | _        |

| RD_L    | t <sub>ar</sub>  | Delay from AS_L asserted           | 23ns | _        |

| AD      | t <sub>rd</sub>  | Delay from RD_L asserted to driven | 40ns | 55ns     |

| RDY_L   | $t_{ryl}$        | Delay from RD_L assertion          | Ons  | infinite |

| RD_L    | t <sub>yr</sub>  | Delay from RDY_L assertion         | Ons  |          |

| AS_L    | t <sub>ya</sub>  | Delay from RDY_L assertion         | 40ns |          |

| AD[7:0] | $t_{ds}$         | Setup time to RDY_L assertion      | Ons  |          |

| AD[7:0] | $t_{dh}$         | Hold time from AS_L deassertion    | 40ns | 55ns     |

| AS_L    | t <sub>aa</sub>  | Minimu deassertion time            | 23ns | _        |

| RDY_L   | t <sub>ryh</sub> | Delay from RD_L deassertion        | 40ns | 55ns     |

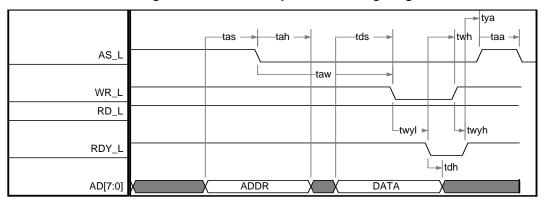

Table 5–8 Diagnostic Port Write Operation Timing Diagram

Table 5–9 Diagnostic Port Write Operation AC Timing

| Signal  | Symbol          | Parameter                      | Min  | Max  |

|---------|-----------------|--------------------------------|------|------|

| AD[3:0] | t <sub>as</sub> | Setup time to AS_L asserted    | 13ns | _    |

| AD[3:0] | t <sub>ah</sub> | Hold time from AS_L asserted   | 23ns | _    |

| AD[7:0] | t <sub>ds</sub> | Setup time to WR_L asserted    | 13ns | _    |

| AD[7:0] | t <sub>dh</sub> | Hold time from RDY_L asserted  | 0ns  | _    |

| WR_L    | $t_{wh}$        | Hold time from RDY_L assertion | Ons  | _    |

| RDY_L   | $t_{\rm wyl}$   | Delay from WR_L assertion      | 40ns | 55ns |

| RDY_L   | $t_{\rm wyh}$   | Delay from WR_L deassertion    | 40ns | 55ns |

| WR_L    | t <sub>aw</sub> | Delay from AS_L assertion      | 36ns | _    |

| AS_L    | t <sub>aa</sub> | Minimum deassertion time       | 23ns | _    |

| AS_L    | t <sub>ya</sub> | Delay from RDY_L deassertion   | Ons  | _    |

#### 5.3.5 JTAG Timing

Table 5-10 JTAG Signal AC TIming Specifications

| Signal   | Symbol            | Parameter      | Min  | Max   |

|----------|-------------------|----------------|------|-------|

| TCK      | F <sub>ftck</sub> | Frequency      | _    | 10MHz |

| TCK      | $T_{tckl}$        | Time low       | 50ns | _     |

| TCK      | $T_{tckh}$        | Time high      | 50ns | _     |

| TDI, TMS | $T_{tsu}$         | Setup to TCK   | 40ns | _     |

| TDI, TMS | $T_{th}$          | Hold from TCK  | 40ns | _     |

| TDO      | T <sub>tval</sub> | Valid from TCK | _    | 30ns  |

| TDO      | $T_{tz}$          | Hi-Z from TCK  | 5ns  | 40ns  |

#### 5.3.6 Asynchronous and Static Signals

Table 5-11 Asynchronous and Static Signals

| Signal                                                                                    | Note                   |

|-------------------------------------------------------------------------------------------|------------------------|

| GPIO[7:0]                                                                                 | Under software control |

| CTAP0[3:0], CTAP1[3:0],<br>RESLO, RESHI                                                   | LVDS control. Static.  |

| BYPASSL, RESETTX,<br>RESETRX, TSTSHFTLD,<br>ECSEL, ETOGGLE, EXDNUP,<br>TSTPHASE, LOOPBKEN | Asynchronous           |

| TESTMODE[4:0]                                                                             | Static                 |

6

# **Contact Information**

### 6.1 Headquarters

Dolphin Interconnect Solution.

7 Boomhower Rd

Woodsville, NH 03785

Voice: (603) 747-4100

Fax: (603) 747-4101

Web: www.dolphinics.com

Email: Info@ dolphinics.com

January 17, 2012 Contact Information 6–25